# Digital Control of High-Frequency Switched-Mode Power Converters

Luca Corradini, Dragan Maksimović Paolo Mattavelli, Regan Zane

# DIGITAL CONTROL OF HIGH-FREQUENCY SWITCHED-MODE POWER CONVERTERS

### **IEEE Press**

445 Hoes Lane Piscataway, NJ 08854

### **IEEE Press Editorial Board**

Tariq Samad, Editor in Chief

George W. Arnold Vladimir Lumelsky Linda Shafer

Dmitry Goldgof Pui-In Mak Zidong Wang

Ekram Hossain Jeffrey Nanzer MengChu Zhou

Mary Lanzerotti Ray Perez George Zobrist

Kenneth Moore, Director of IEEE Book and Information Services (BIS)

### **Technical Reviewers**

Francisco J. Azcondo, *Universidad de Cantabria*Fujio Kurokawa, *Nagasaki University*Jian Sun, *Rensselaer Polytechnic Institute*

# DIGITAL CONTROL OF HIGH-FREQUENCY SWITCHED-MODE POWER CONVERTERS

LUCA CORRADINI DRAGAN MAKSIMOVIĆ PAOLO MATTAVELLI REGAN ZANE

Copyright © 2015 by The Institute of Electrical and Electronics Engineers, Inc.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. All rights reserved Published simultaneously in Canada

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

#### Library of Congress Cataloging-in-Publication Data:

Corradini, Luca.

Digital control of high-frequency switched-mode power converters / Luca Corradini, Dragan Maksimovic, Paolo Mattavelli, Regan Zane.

pages cm

Includes bibliographical references and index.

ISBN 978-1-118-93510-1 (cloth)

- 1. Electric current converters—Automatic control. 2. Switching power supplies—Automatic control.

- 3. Digital control systems. I. Maksimovic, Dragan, 1961- II. Mattavelli, Paolo. III. Zane, Regan. IV. Title. TK2796.C67 2015

621.381'044-dc23

2014033408

Printed in the United States of America

10987654321

# **CONTENTS**

| PREF. | ACE<br>DDUCTION                                                                                                           | ix<br>1 |

|-------|---------------------------------------------------------------------------------------------------------------------------|---------|

| СНАРТ | TER 1 CONTINUOUS-TIME AVERAGED MODELING OF DC-DC CONVERTERS                                                               | 13      |

| 1.1   | Pulse Width Modulated Converters 14                                                                                       |         |

| 1.2   | Converters in Steady State 16                                                                                             |         |

|       | 1.2.1 Boost Converter Example 17                                                                                          |         |

|       | 1.2.2 Estimation of the Switching Ripple 19                                                                               |         |

|       | 1.2.3 Voltage Conversion Ratios of Basic Converters 20                                                                    |         |

| 1.3   | Converter Dynamics and Control 21                                                                                         |         |

|       | 1.3.1 Converter Averaging and Linearization 22                                                                            |         |

|       | 1.3.2 Modeling of the Pulse Width Modulator 24                                                                            |         |

|       | 1.3.3 The System Loop Gain 25                                                                                             |         |

|       | 1.3.4 Averaged Small-Signal Models of Basic Converters 26                                                                 |         |

| 1.4   | State-Space Averaging 28                                                                                                  |         |

|       | 1.4.1 Converter Steady-State Operating Point 28                                                                           |         |

|       | 1.4.2 Averaged Small-Signal State-Space Model 29 1.4.3 Boost Converter Example 30                                         |         |

| 1.5   | 1.4.3 Boost Converter Example 30 Design Examples 32                                                                       |         |

| 1.5   | 1.5.1 Voltage-Mode Control of a Synchronous Buck Converter 32                                                             |         |

|       | 1.5.1 Voltage-Mode Control of a Synchronous Buck Converter 32  1.5.2 Average Current-Mode Control of a Boost Converter 42 |         |

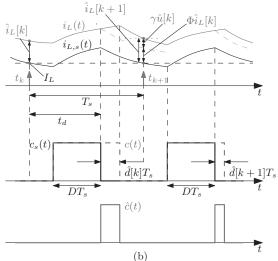

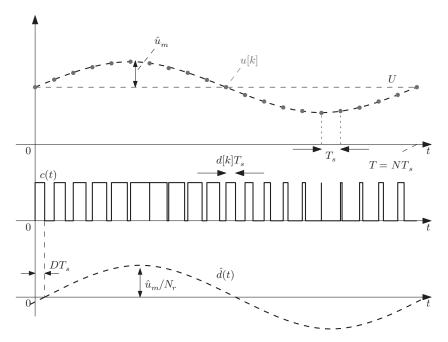

| 1.6   | Duty Ratio $d[k]$ Versus $d(t)$ 48                                                                                        |         |

| 1.7   | Summary of Key Points 50                                                                                                  |         |

| 1.7   | Summary of Rey Forms 30                                                                                                   |         |

| СНАРТ | TER 2 THE DIGITAL CONTROL LOOP                                                                                            | 51      |

| 2.1   | Case Study: Digital Voltage-Mode Control 52                                                                               |         |

| 2.2   | A/D Conversion 53                                                                                                         |         |

|       | 2.2.1 Sampling Rate 53                                                                                                    |         |

|       | 2.2.2 Amplitude Quantization 56                                                                                           |         |

| 2.3   | The Digital Compensator 58                                                                                                |         |

| 2.4   | Digital Pulse Width Modulation 63                                                                                         |         |

| 2.5   | Loop Delays 65                                                                                                            |         |

|       | 2.5.1 Control Delays 65                                                                                                   |         |

|       | 2.5.2 Modulation Delay 66                                                                                                 |         |

|       | 2.5.3 Total Loop Delay <b>70</b>                                                                                          |         |

| 2.6   | Use of Averaged Models in Digital Control Design 71                                                                       |         |

|       | 2.6.1     | Limitations of Averaged Modeling 71                                  |     |

|-------|-----------|----------------------------------------------------------------------|-----|

|       | 2.6.2     | Averaged Modeling of a Digitally Controlled Converter 74             |     |

| 2.7   | Summary   | y of Key Points 78                                                   |     |

| СНАРТ | ER 3 DI   | ISCRETE-TIME MODELING                                                | 79  |

| 3.1   | Discrete- | Time Small-Signal Modeling 80                                        |     |

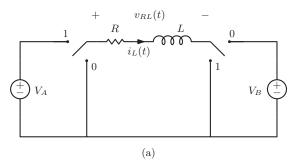

|       | 3.1.1     | A Preliminary Example: A Switched Inductor 82                        |     |

|       | 3.1.2     | The General Case 85                                                  |     |

|       | 3.1.3     | Discrete-Time Models for Basic Types of PWM Modulation 87            |     |

| 3.2   | Discrete- | Time Modeling Examples 88                                            |     |

|       | 3.2.1     |                                                                      |     |

|       | 3.2.2     | Boost Converter 97                                                   |     |

| 3.3   | Discrete- | Time Modeling of Time-Invariant Topologies 102                       |     |

|       |           | Equivalence to Discrete-Time Modeling 106                            |     |

|       |           | Relationship with the Modified Z-Transform 108                       |     |

|       | 3.3.3     | Calculation of $T_u(z)$ 108                                          |     |

|       |           | Buck Converter Example Revisited 112                                 |     |

| 3.4   | Matlab®   | Discrete-Time Modeling of Basic Converters 112                       |     |

| 3.5   | Summary   | y of Key Points 117                                                  |     |

|       |           |                                                                      |     |

| CHAPT | ER 4 DI   | IGITAL CONTROL                                                       | 119 |

| 4.1   | System-I  | Level Compensator Design 119                                         |     |

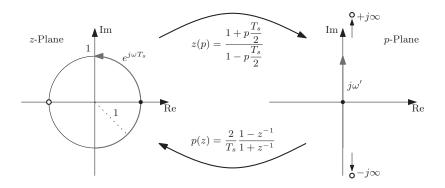

|       | 4.1.1     | Direct-Digital Design Using the Bilinear Transform Method 120        |     |

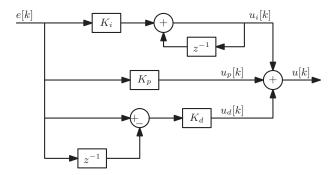

|       | 4.1.2     | Digital PID Compensators in the $z$ - and the $p$ -Domains 123       |     |

| 4.2   | Design E  |                                                                      |     |

|       |           | Digital Voltage-Mode Control of a Synchronous Buck Converter         | 126 |

|       |           | Digital Current-Mode Control of a Boost Converter 134                |     |

|       |           | Multiloop Control of a Synchronous Buck Converter 136                |     |

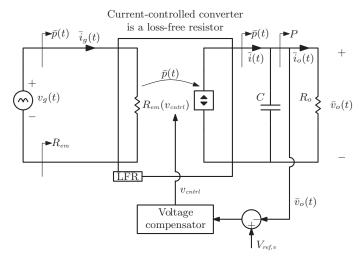

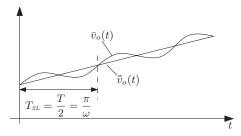

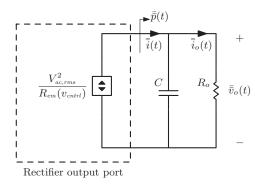

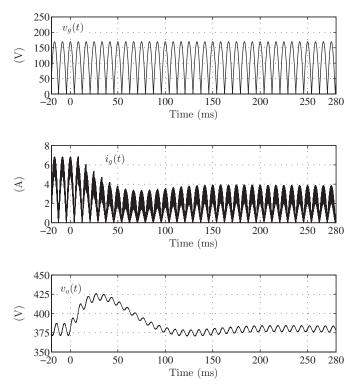

|       | 4.2.4     | Boost Power Factor Corrector 141                                     |     |

| 4.3   | Other Co  | onverter Transfer Functions 154                                      |     |

| 4.4   | Actuator  | Saturation and Integral Anti-Windup Provisions 160                   |     |

| 4.5   |           | y of Key Points 165                                                  |     |

| CHAPT | ED 5 AN   | MPLITUDE QUANTIZATION                                                | 167 |

| CHAIT | LK 3 7171 | H BH ODE GOMMIZHION                                                  | 107 |

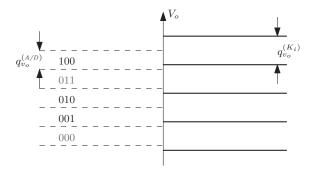

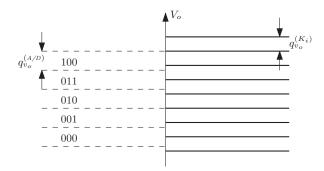

| 5.1   | System C  | Quantizations 167                                                    |     |

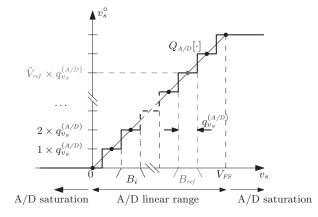

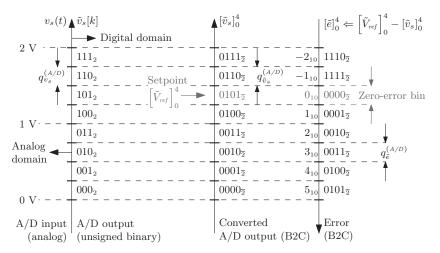

|       | 5.1.1     | A/D Converter 167                                                    |     |

|       |           | DPWM Quantization 169                                                |     |

| 5.2   |           | tate Solution 172                                                    |     |

| 5.3   |           | t-Cycling Conditions 175                                             |     |

|       | 5.3.1     | DPWM versus A/D Resolution 175                                       |     |

|       | 5.3.2     | Integral Gain 178                                                    |     |

|       | 5.3.3     | Dynamic Quantization Effects 181                                     |     |

| 5.4   |           | and A/D Implementation Techniques 182                                |     |

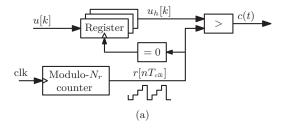

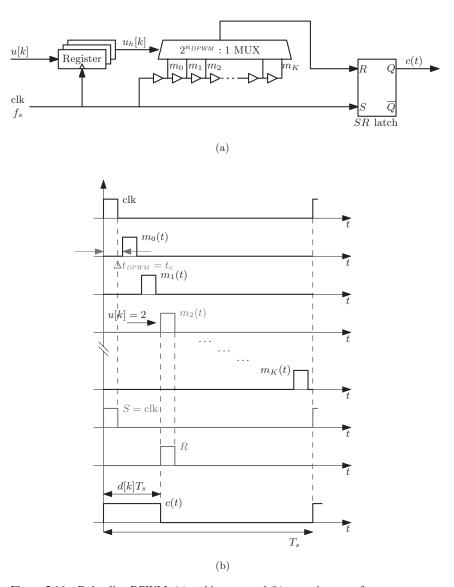

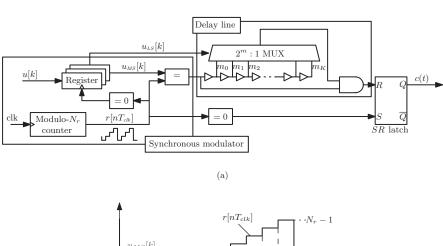

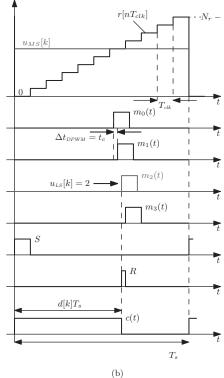

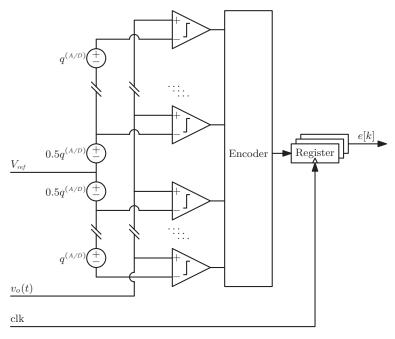

|       | 5.4.1     | DPWM Hardware Implementation Techniques 182                          |     |

|       | 5.4.2     | Effective DPWM Resolution Improvements via $\Sigma\Delta$ Modulation | 186 |

| CILLER | COMPENSATOR IMPLEMENTATION                                           | 40. |

|--------|----------------------------------------------------------------------|-----|

| СНАРТ  | TER 6 COMPENSATOR IMPLEMENTATION                                     | 19  |

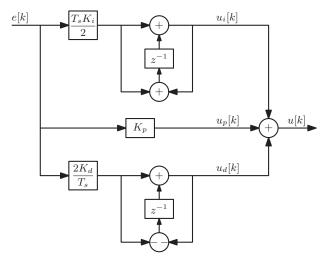

| 6.1    | PID Compensator Realizations 194                                     |     |

| 6.2    | Coefficient Scaling and Quantization 197                             |     |

|        | 6.2.1 Coefficients Scaling 198                                       |     |

|        | 6.2.2 Coefficients Quantization 200                                  |     |

| 6.3    | Voltage-Mode Control Example: Coefficients Quantization 203          |     |

|        | 6.3.1 Parallel Structure 204                                         |     |

|        | 6.3.2 Direct Structure <b>206</b>                                    |     |

|        | 6.3.3 Cascade Structure 208                                          |     |

| 6.4    | Fixed-Point Controller Implementation 213                            |     |

|        | 6.4.1 Effective Dynamic Range and Hardware Dynamic Range 214         |     |

|        | 6.4.2 Upper Bound of a Signal and the $L^1$ -Norm 216                |     |

| 6.5    | Voltage-Mode Converter Example: Fixed-Point Implementation 218       |     |

|        | 6.5.1 Parallel Realization 220                                       |     |

|        | 6.5.2 Direct Realization 225                                         |     |

|        | 6.5.3 Cascade Realization 229                                        |     |

|        | 6.5.4 Linear versus Quantized System Response 233                    |     |

| 6.6    | HDL Implementation of the Controller 234                             |     |

|        | 6.6.1 VHDL Example 235                                               |     |

|        | 6.6.2 Verilog Example 237                                            |     |

| 6.7    | Summary of Key Points 239                                            |     |

|        |                                                                      |     |

| CHAPT  | TER 7 DIGITAL AUTOTUNING                                             | 24  |

| 7.1    | Introduction to Digital Autotuning 242                               |     |

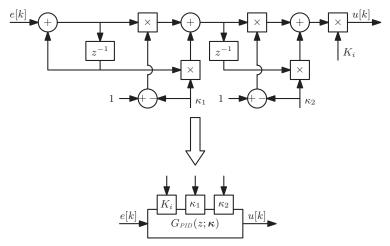

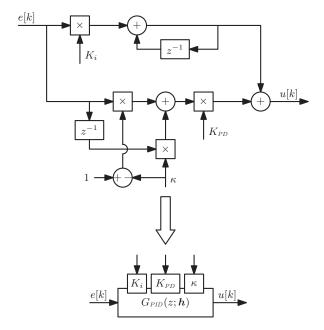

| 7.2    | Programmable PID Structures 243                                      |     |

| 7.3    | Autotuning VIA Injection of a Digital Perturbation 247               |     |

|        | 7.3.1 Theory of Operation 249                                        |     |

|        | 7.3.2 Implementation of a PD Autotuner 253                           |     |

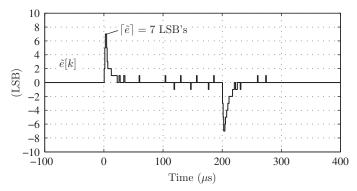

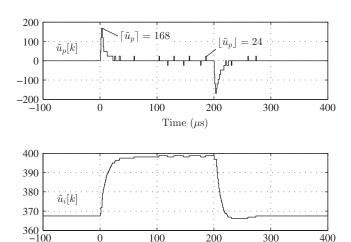

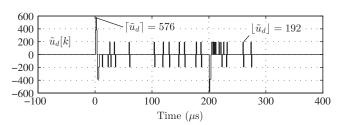

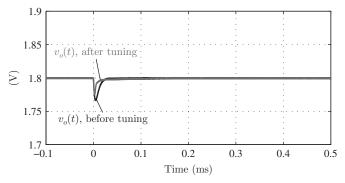

|        | 7.3.3 Simulation Example 255                                         |     |

|        | 7.3.4 Small-Signal Analysis of the PD Autotuning Loop 261            |     |

| 7.4    | Digital Autotuning Based on Relay Feedback 265                       |     |

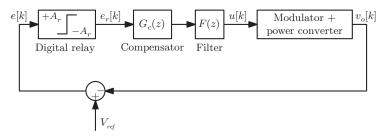

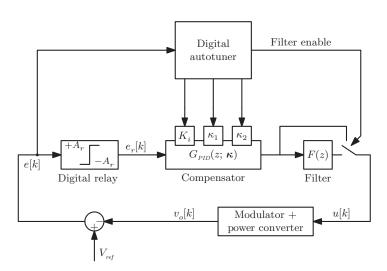

|        | 7.4.1 Theory of Operation <b>266</b>                                 |     |

|        | 7.4.2 Implementation of a Digital Relay Feedback Autotuner 267       |     |

|        | 7.4.3 Simulation Example <b>271</b>                                  |     |

| 7.5    | Implementation Issues 272                                            |     |

| 7.6    | Summary of Key Points 275                                            |     |

| APPEN  | DIX A DISCRETE-TIME LINEAR SYSTEMS AND THE Z-TRANSFORM               | 27  |

| A.1    | Difference Equations 277                                             |     |

| Α.1    | A.1.1 Forced Response 278                                            |     |

|        | A.1.2 Free Response 279                                              |     |

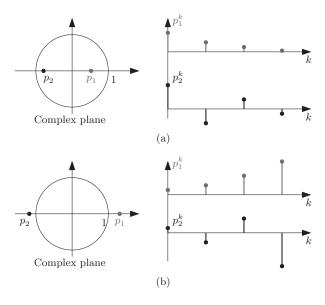

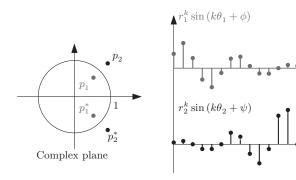

|        | A.1.2 Prec Response 279  A.1.3 Impulse Response and System Modes 281 |     |

|        | A.1.4 Asymptotic Behavior of the Modes 282                           |     |

|        | A.1.5 Further Examples 283                                           |     |

|        | 11.1.0 1 druier Examples 200                                         |     |

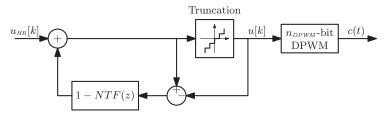

5.4.3 A/D Converters **187**

### viii CONTENTS

| A.2                                     | Z-Transform 284                                              |     |

|-----------------------------------------|--------------------------------------------------------------|-----|

|                                         | A.2.1 Definition 284                                         |     |

|                                         | A.2.2 Properties 285                                         |     |

| A.3                                     | The Transfer Function 287                                    |     |

|                                         | A.3.1 Stability 287                                          |     |

|                                         | A.3.2 Frequency Response 288                                 |     |

| A.4                                     | State-Space Representation 288                               |     |

|                                         | TWEN DOINT A DITHMETIC AND UDL CODING                        |     |

| APPEN                                   | DIX B FIXED-POINT ARITHMETIC AND HDL CODING                  | 291 |

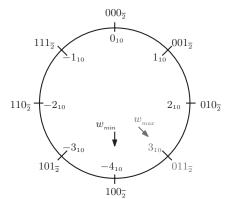

| B.1                                     | Rounding Operation and Round-Off Error 291                   |     |

| B.2                                     | Floating-Point versus Fixed-Point Arithmetic Systems 293     |     |

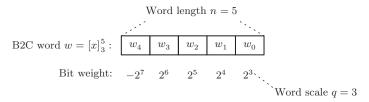

| B.3                                     | Binary Two's Complement (B2C) Fixed-Point Representation 294 |     |

| B.4                                     | Signal Notation 296                                          |     |

| B.5                                     | Manipulation of B2C Quantities and HDL Examples 297          |     |

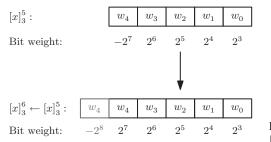

|                                         | B.5.1 Sign Extension 298                                     |     |

|                                         | B.5.2 Alignment 299                                          |     |

|                                         | B.5.3 Sign Reversal <b>301</b>                               |     |

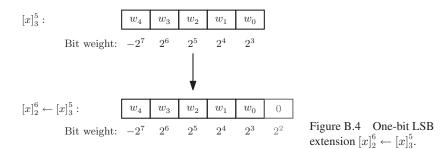

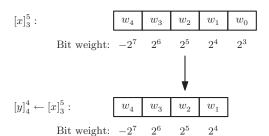

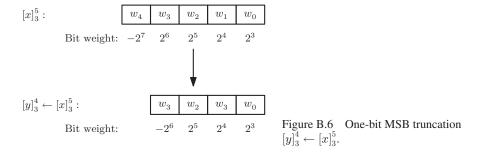

|                                         | B.5.4 LSB and MSB Truncation 302                             |     |

|                                         | B.5.5 Addition and Subtraction 304                           |     |

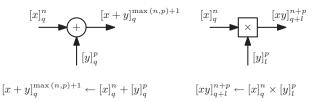

|                                         | B.5.6 Multiplication 305                                     |     |

|                                         | B.5.7 Overflow Detection and Saturated Arithmetic 307        |     |

| APPEN                                   | DIX C SMALL-SIGNAL PHASE LAG OF UNIFORMLY SAMPLED PULSE      |     |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | WIDTH MODULATORS                                             | 313 |

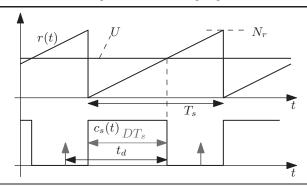

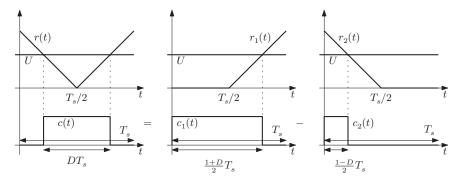

| C.1                                     | Trailing-Edge Modulators 313                                 |     |

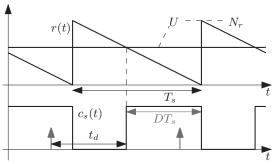

| C.2                                     | Leading-Edge Modulators 317                                  |     |

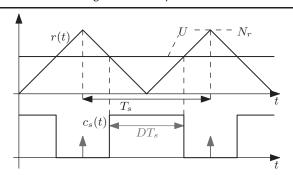

| C.3                                     | Symmetrical Modulators 318                                   |     |

| RFFF                                    | RENCES                                                       | 321 |

|                                         |                                                              |     |

| INDE                                    | X                                                            | 335 |

|                                         |                                                              |     |

# PREFACE

Power electronics fundamentals have been established within the framework of continuous-time analysis, averaged modeling of switched-mode power converters, and analog control theory [1–5]. Ever more often, control and management functions around power converters are implemented digitally, expanding the field of fundamentals to discrete-time modeling and digital control concepts specific to power electronics. Standard textbooks and courses dedicated to digital control of dynamic systems in general provide the necessary background but seldom, if ever, address the specifics necessary to fully understand and successfully practice the design of digitally controlled power converters. We attempt, in this book, to fill the gap by treating the fundamental aspects of digital control of high-frequency switched-mode power converters in a systematic and rigorous manner. Our objectives are to put the reader in the position to understand, analyze, model, design, and implement digital feedback loops around power converters, from system-level transfer function formulations to coding practical designs in one of the mainstream hardware description languages (HDLs) such as VHDL or Verilog.

The book is intended for graduate students of electrical engineering pursuing a curriculum in power electronics and as a reference for engineers and researchers who seek to expand on the expertise in design-oriented knowledge of digital control of power electronics. It is assumed that the reader is well acquainted with foundations of the power electronics discipline, along with associated continuous-time modeling and control techniques [1–6]. Familiarity with sampled-data and discrete-time system analysis topics is helpful but not absolutely essential. Key concepts are developed from the beginning, including a brief review of the necessary discrete-time system fundamentals in Appendix A. For a more comprehensive background, the reader is referred to one of the standard textbooks, such as [7, 8].

The book is composed of eight chapters, structured as follows. The introductory chapter provides an overview of digital control of high-frequency switched-mode power converters, the motivation behind the surge of interest in the area, a summary of analysis, modeling, control, and implementation issues, as well as a summary of recent advances demonstrating potential advantages of digital controllers, including system power management interfaces, programmability of control functions, dynamic response and efficiency improvements, and practical autotuning techniques.

Chapter 1 provides a review of the continuous-time averaged modeling approach for switched-mode power converters. Averaged small-signal modeling is extensively covered by a number of authoritative textbooks [1–3], and the intention is not to replicate this subject in its entirety. Rather, the purpose of Chapter 1 is to focus the reader's attention on the methodology and *assumptions* behind the averaging approach. Understanding of the philosophy and limitations of the

averaging technique is essential to appreciate the need for a different approach when it comes to digitally controlled converters.

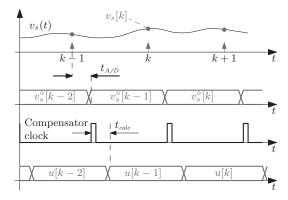

Chapter 2 introduces the main elements of a digitally controlled converter, with the purpose of providing the reader with a quick overview of the main differences between analog and digital control without immediately entering into detailed modeling issues. This chapter ends with a discussion about the use of continuous-time averaged modeling for designing digital loops, an approach often employed in practice but which can only account for sampling effects and digital control delays in an approximate manner.

The discussion motivates the formulation of a *discrete-time* modeling approach, developed in Chapter 3, which correctly treats the digitally controlled converter as a sampled-data system and formulates its small-signal dynamics in the z-domain rather than in the Laplace domain. In addition to providing the theoretical framework of discrete-time modeling, a number of modeling examples are discussed in Chapter 3. Furthermore, it is shown that a direct link can be established between continuous-time modeling and discrete-time modeling for the converters that are *topologically invariant*, such as the Buck converter. In such cases, a simple and straightforward discretization rule can be formulated, which translates the converter averaged small-signal model into the exact discrete-time model.

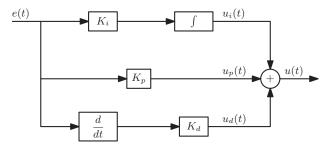

Chapter 4 is devoted to direct digital compensator design, based on the discrete-time models developed in Chapter 3. Among many techniques discussed in the literature, the emphasis is given here to the so-called bilinear transform method. The main advantage of the approach is that the entire design procedure is formulated in an equivalent continuous-time domain, in which both the digitally controlled converter and the compensator under design assume the form of continuous-time systems. As a result, the direct digital design can take advantage of the familiar analog control design techniques with the design specifications formulated in the frequency domain. Standard digital proportional-integral (PI) and proportional-integral-derivative (PID) compensator designs are addressed in a number of examples, including voltage-mode, current-mode, and multiloop control of dc-dc converters and power factor correction (PFC) rectifiers.

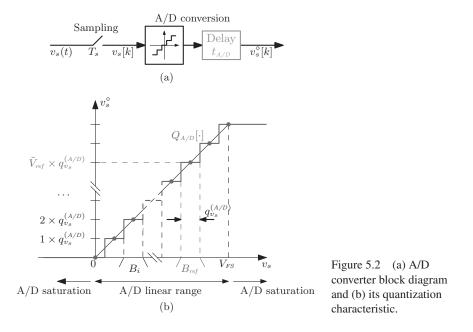

Amplitude quantization effects introduced by analog-to-digital (A/D) converters and digital pulse width modulators (DPWMs) are discussed in Chapter 5. This chapter first clarifies how limit cycle oscillations can arise in a digitally controlled dc—dc converter in relation to the existence of a dc operating point for the closed-loop system. Secondly, basic design guidelines—referred to as *no-limit-cycling conditions*—are presented, which aim at preventing such generally undesired phenomena to occur. This chapter ends with a brief overview of DPWM and A/D architectures and associated implementation trade-offs.

The issue of compensator implementation is covered in Chapter 6. Scaling and quantization of compensator coefficients are treated first, with the goal of quantifying the quantization-induced errors on the loop gain magnitude and phase at the desired crossover frequency. Secondly, this chapter addresses implementation of the control law in a fixed-point arithmetic environment, providing a methodology for word length determination of the various signals inside the control structure. Given the focus of the book on high-frequency switched-mode power converter applications, the emphasis

is on *hardwired* implementations of the control law, together with VHDL and Verilog coding examples. Nevertheless, the principles that apply to software-based, microprogrammed realizations are highlighted as well.

Autotuning is an advanced application of digital control, which brings up intriguing potentials and additional challenges. Because of the importance of this emerging topic, Chapter 7 is devoted to an overview of digital autotuning techniques for high-frequency switched-mode power converters. After a brief discussion about digital autotuning basics, two autotuning techniques are presented in more detail: an injection-based approach and a relay-based approach.

An objective in writing the book has been to emphasize the distinction between the fundamental, theoretical aspects of digital control design on one side and the application of these techniques on the other, demystifying the perception about discrete-time models or digital control as being exceedingly complex and difficult to employ in practice. In line with such philosophy, Matlab® script examples are systematically developed alongside the theory. A few Matlab® commands allow, in most situations, to straightforwardly carry out system-level compensator designs and rapidly proceed to HDL coding and implementation steps. Furthermore, throughout the book, a number of design examples are fully worked out and verified by simulations in the Matlab® environment.

# INTRODUCTION

Efficient processing and control of electric power is required in applications ranging from submilliwatt on-chip power management to hundreds of kilowatt and megawatt power levels in motor drives and utility applications. The objectives of high efficiency, as well as static and dynamic control of inputs or outputs under a range of operating conditions, are accomplished using power electronics, that is, switched-mode power converters consisting of passive (capacitive and inductive) components, and power semiconductor devices operated as switches. In high-power applications, control and monitoring tasks are often more complex, while the power semiconductor devices are operated at relatively low switching frequencies, for example, up to tens of kilohertz. The controller cost and power consumption are relatively low compared to the overall system cost and power rating. In these applications, digital control offers clear technical and economic advantages in addressing complex control, management, and monitoring tasks. As a result, for many years now, digital control methods and digital controllers based on general-purpose or dedicated microprocessors, digital signal processor (DSPs), or programmable logic devices have been widely adopted in power electronics applications at relatively high power levels.

In ubiquitous low-to-medium power switched-mode power supply (SMPS) applications, including point-of-load (POL) regulators, nonisolated and isolated dc–dc converters, single-phase power factor correction (PFC) rectifiers, single-phase inverters, and lighting applications, adoption of digital power management and digital control has been slower. In these applications, switching frequencies are often in the range from hundreds of kilohertz to multiple megahertz, and much faster dynamic responses are required. The controller cost and the controller power consumption can easily present significant portions of the system cost and power dissipation. Furthermore, in many applications, control challenges have been successfully met by continuous advances of readily available analog controllers, using well-established analog analysis, modeling, and design techniques [1–5]. Nevertheless, practical digital control of high-frequency switched-mode power converters has moved from proof-of-concept demonstrations to digital pulse width modulation (DPWM) controller chips commercially available from multiple vendors, with growing adoption rates in many applications. Several factors have

contributed to the increasing penetration of the concept of "digital power" in high-frequency power electronics applications:

- Ongoing advances in digital integrated-circuit processes have continued to increase processing capabilities while bringing the cost down.

- The needs for improved system integration and increasingly complex power management and monitoring functions have translated into the needs for digital interfaces and programmability in switched-mode power conversion applications [9–11].

- Practical high-performance digital control techniques have been introduced and demonstrated, together with innovative approaches offering performance gains or entirely new capabilities that would be difficult or impractical to realize using traditional analog techniques [12–14].

The "digital power" concept encompasses several aspects:

- 1. Digital power management, which refers to system-level control and monitoring of power conversion and distribution, usually over a serial communication bus [9–11]. Power management functions include turning on and off or sequencing system power rails, adjusting setpoints for converter control loops, programming control loop parameters, monitoring and reporting of measured status or variables, and so on [15, 16]. These functions are typically performed at timescales that are relatively long compared to a switching period.

- **2.** *Digital control*, which includes time-domain and frequency-domain converter modeling and control techniques, with control actions performed at timescales comparable to a switching period.

- **3.** *Digital implementation techniques*, which can be classified into two main groups:

- Software-based controllers, where control algorithms are designed and implemented in code executed on general-purpose or specialized microcontrollers or DSP chips. An early example of application of microprogrammed digital control to power factor preregulators is presented in [17].

- Hardware-based controllers, based on custom-integrated circuits or programmable logic devices such as field-programmable gate arrays (FPGAs) [18, 19]. Early examples of such hardware-based digital controllers can be found in [20–22].

This book is focused on the fundamental aspects of analysis, modeling, and design of digital control loops around high-frequency switched-mode power converters in a systematic and rigorous manner. The objectives are to enable the reader to understand, analyze, model, design, and implement digital feedback loops around power converters, from system-level transfer function formulations to practical implementation details. The purpose of this chapter is to introduce the topics covered in the book and to motivate the reader to pursue the theoretical and practical concepts covered in the remaining chapters of this book. Furthermore, this introductory chapter points to some of the more advanced digital techniques reported in the literature, including

approaches to dynamic response improvements, system identification, autotuning of digital control loops, and on-line efficiency optimization.

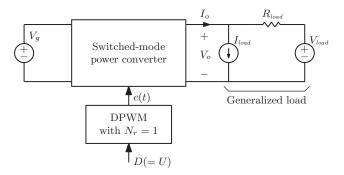

# DIGITALLY CONTROLLED SWITCHED-MODE CONVERTERS

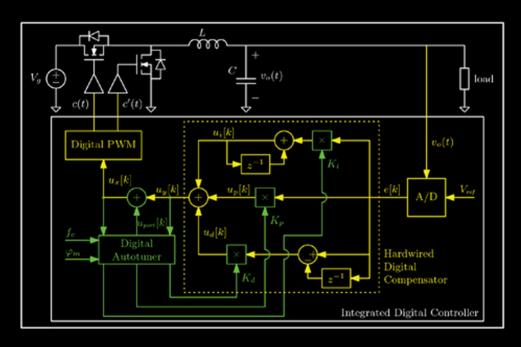

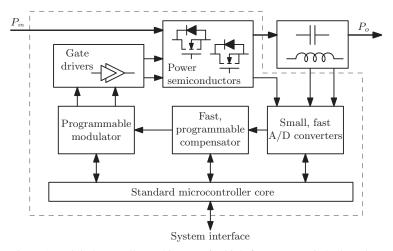

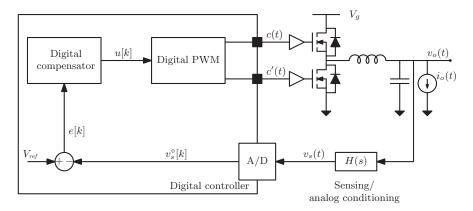

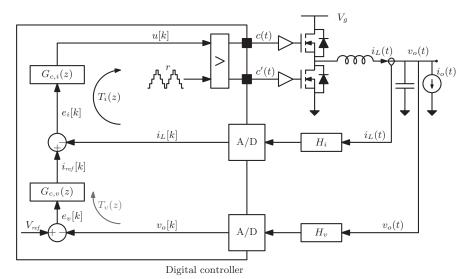

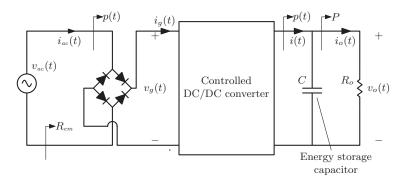

A number of DPWM controller architectures and implementation strategies have been investigated and realized in practice. Many standard microcontrollers and DSP chips are now available, featuring multiple high-resolution PWM and analog-to-digital (A/D) channels, which allow software-based implementation of control and management functions. While advances in this area have been rapid, the software-based approaches are still better suited for applications where switching converters operate at relatively low switching frequencies. On the other hand, at switching frequencies in the hundreds of kilohertz to megahertz range, specialized hardware-based control loops are often preferred. This approach is illustrated in the architecture shown in Fig. 1 [12, 13]. The control loop is digital, using specialized, programmable A/D, DPWM, and compensator blocks to achieve high-performance closed-loop dynamic responses, while programmability, power management, and system interface functions are delegated to a microcontroller core. Similar combinations of programmable hardware peripherals specialized for switched-mode power converter applications, with software-based realizations of higher-level management and communication functions are often found in commercially available DPWM controllers.

Controllers of the type shown in Fig. 1 can be developed, realized, and tested using standard digital VLSI design flow starting from logic functions described using

Figure 1 Digital controller architecture for high-frequency switched-mode power converters [13].

#### 4 INTRODUCTION

hardware description language (VHDL or Verilog), followed by prototyping and experimental verifications using FPGA development platforms, ultimately targeting relatively small, relatively low-gate-count integrated circuits capable of matching or surpassing the state-of-the-art analog solutions in terms of dynamic performance, power consumption, and cost. At the same time, digital PWM controllers offer digital system interface, programmability and flexibility, power management functions, reductions in the number of passive components, reduced sensitivity to process and temperature variations, and potentials for practical realizations of more advanced features.

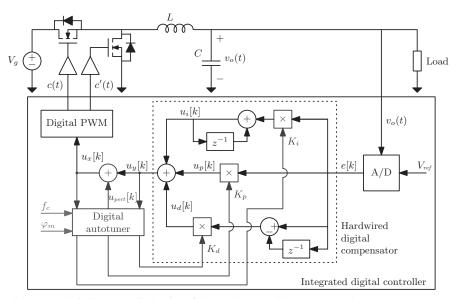

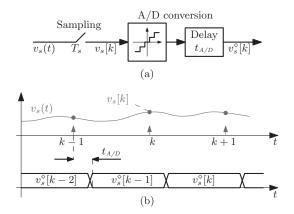

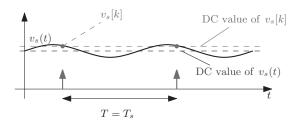

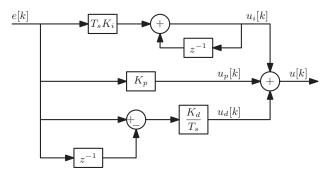

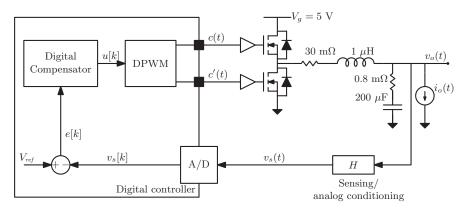

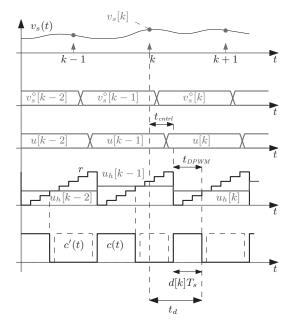

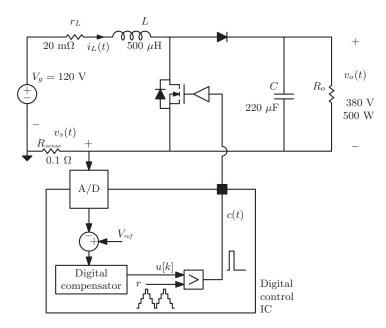

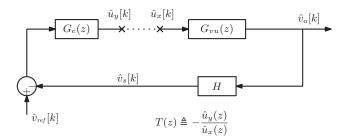

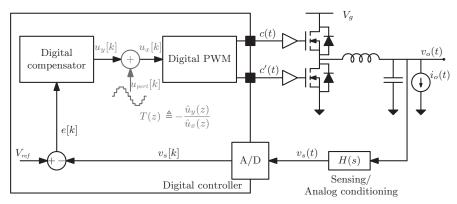

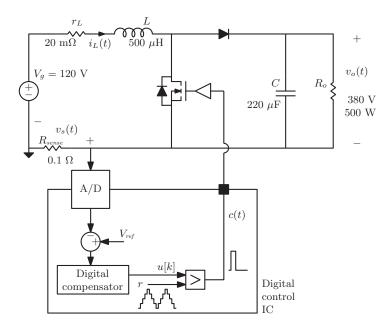

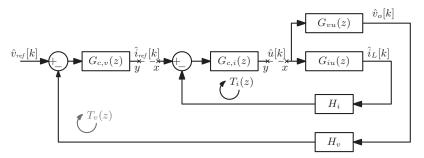

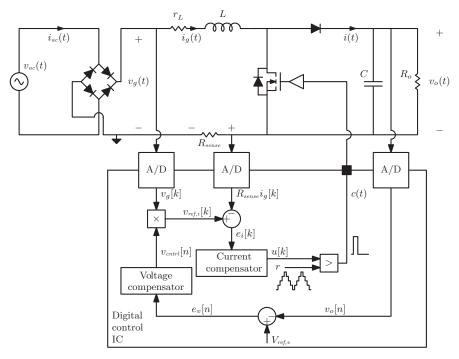

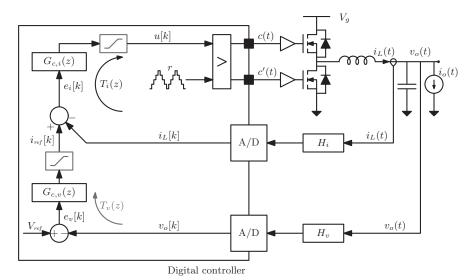

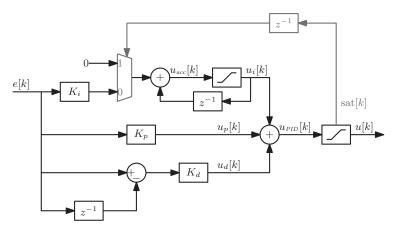

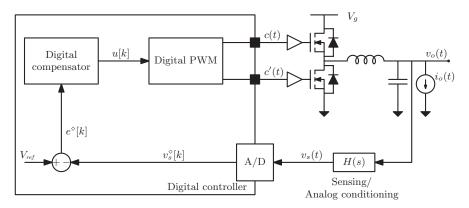

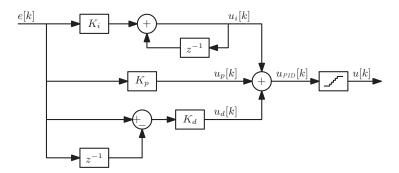

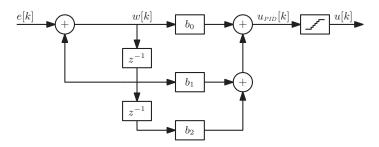

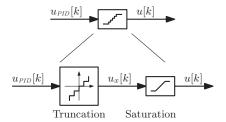

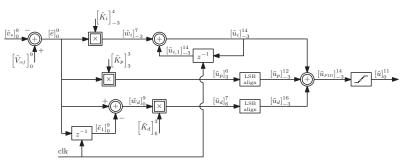

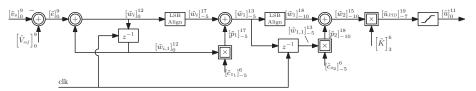

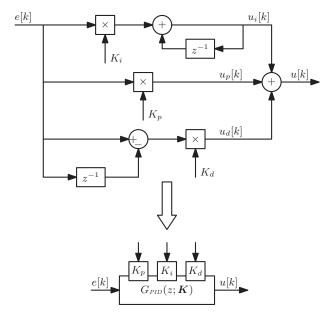

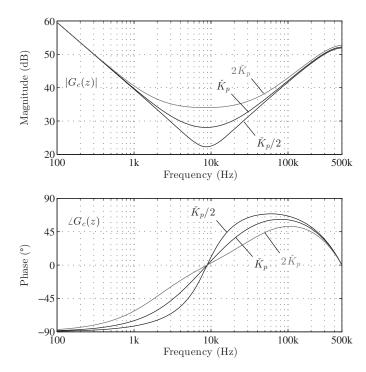

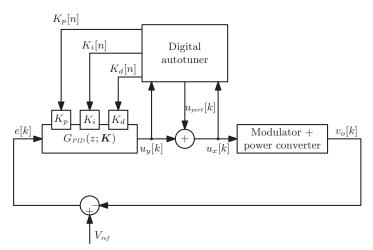

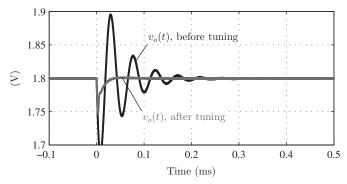

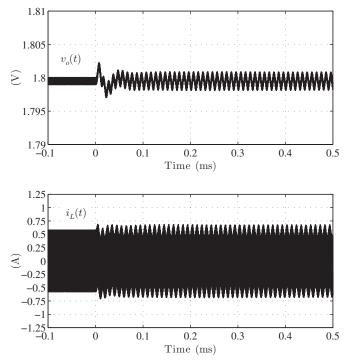

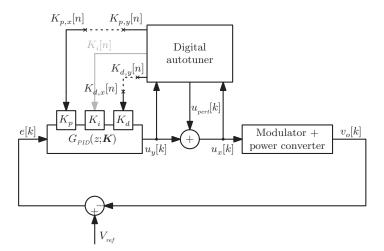

Figure 2 shows a more detailed block diagram of a hardware-based digital controller around a POL synchronous Buck converter. Output voltage  $v_o(t)$  is sampled by an A/D converter and compared to a setpoint reference  $V_{ref}$  to produce a digital voltage error signal e[k]. The error signal is processed by a discrete-time digital proportional-integral-derivative (PID) compensator to generate a duty cycle command  $u_x[k]$ . In the basic version of the controller, the compensator gains  $K_p, K_i$ , and  $K_d$  are found by design to meet control loop specifications, such as the crossover frequency and phase margin, as detailed in Chapters 1–6 of this book. Once a compensator is designed, the gains can be realized using digital multipliers, as shown in Fig. 2. As only a few bits are sufficient to represent the error signal e[k], the entire compensator can also be implemented as a lookup table [21–24]. In a more advanced case, as illustrated by the digital autotuner block in Fig. 2, the compensator gains can

Figure 2 Digitally controlled point-of-load (POL) synchronous Buck dc-dc converter example. Analysis, modeling, design, and implementation of digital control loops are addressed in Chapters 1–6. An additional injection-based autotuning block is shown, which is further discussed in Chapter 7.

be tuned in response to the actual system dynamics to meet the desired specifications. Autotuning is addressed in Chapter 7. Finally, a DPWM block generates the complementary gate-drive control signals c(t) and c'(t) with duty cycle set by the digital command and with appropriate dead times. Together with various enhancements, such a controller can be realized in about 10,000 equivalent logic gates, which translates to about one-third of a square millimeter in a standard 0.35  $\mu m$  CMOS process. Furthermore, higher-density CMOS processes with high-voltage extensions suitable for power electronics applications are now readily available, making power and cost-effective digital controllers for high-frequency switched-mode power converters a reality. Examples of integrated digital controllers can be found in [21, 22, 24–33].

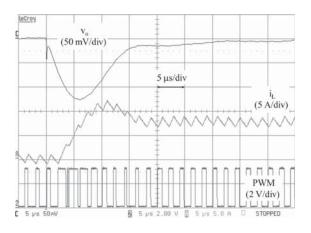

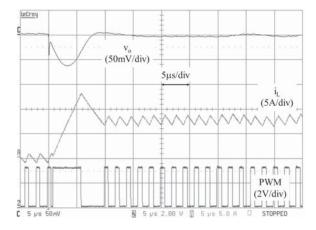

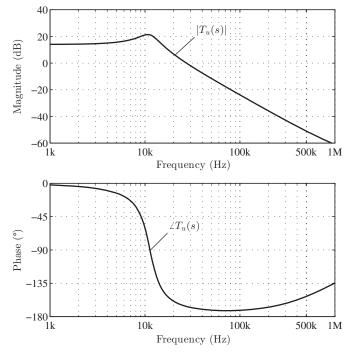

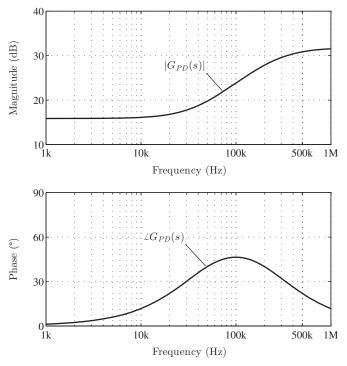

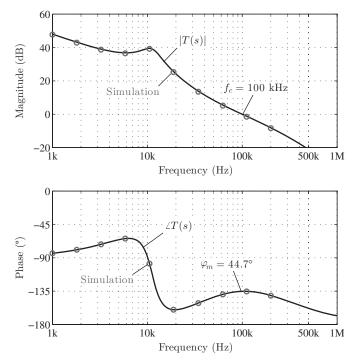

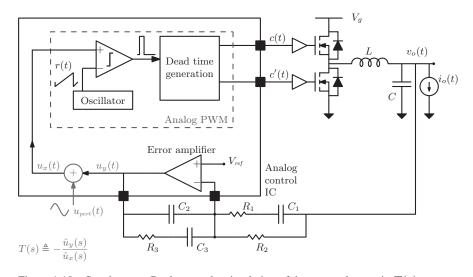

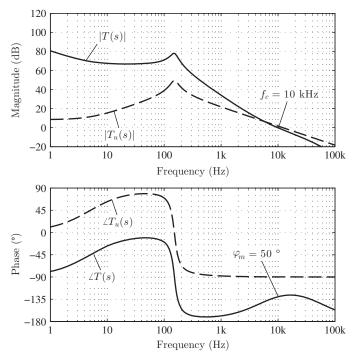

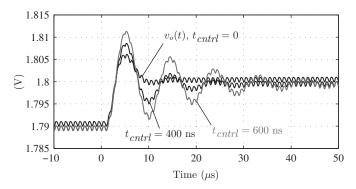

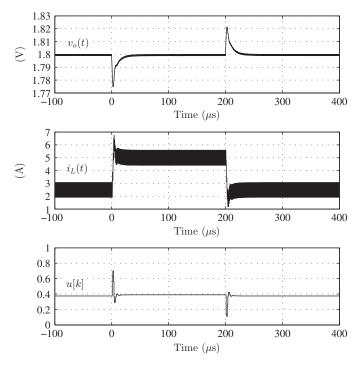

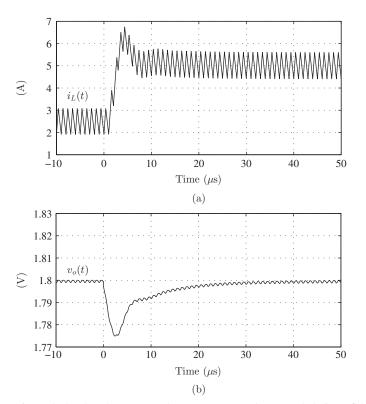

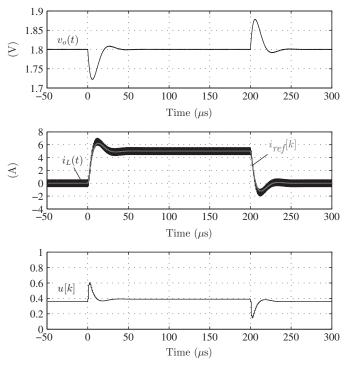

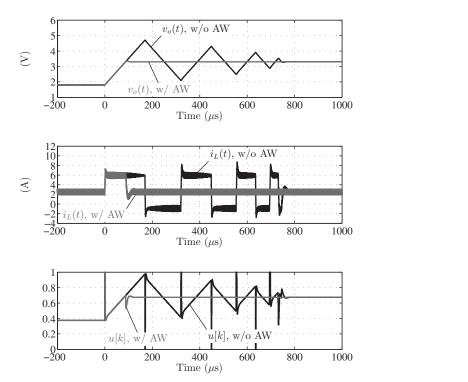

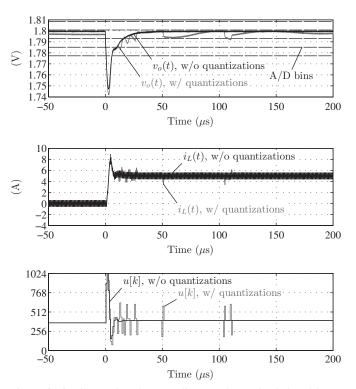

It is of interest to examine a practical example. Following the block diagram shown in Fig. 2 (without the digital autotuner), a digitally controlled 5 to 1.6 V synchronous Buck converter prototype is described in [34]. The filter component values are  $L=1.1~\mu\mathrm{H},\,C=250~\mu\mathrm{F},$  and the switching frequency is  $500~\mathrm{kHz}.$  The A/D converter is a windowed converter [26], using threshold inverter quantization approach [35]. The A/D conversion range is approximately  $200~\mathrm{mV},$  centered around the reference  $V_{ref}=1.6~\mathrm{V},$  for an equivalent output voltage quantization step of 3 mV. A hybrid counter/ring oscillator DPWM is employed, with a time quantization of about 390 ps, that is, with 0.02% duty cycle resolution. A digital PID compensator designed for  $f_c\approx f_s/10=100~\mathrm{kHz}$  crossover frequency is VHDL coded and implemented on an FPGA. Figure 3 illustrates an experimental 0 to 8 A load step response, with the voltage deviation and the response time comparable to responses expected from high-performance analog PWM controllers.

### Analysis, Modeling, and Control Techniques

Referring to the example in Fig. 2, one may observe that the basic digital control loop is conceptually similar to the standard voltage-mode analog PWM control

Figure 3 Experimental 0 to 8 A load step response in a digitally controlled POL Buck converter with conventional PID compensation [34]  $(v_o, 50 \text{ mV/div}; i_L, 5 \text{ A/div}; \text{ and timescale}, 5 \text{ } \mu\text{s/div})$ . © 2009 IEEE.

#### 6 INTRODUCTION

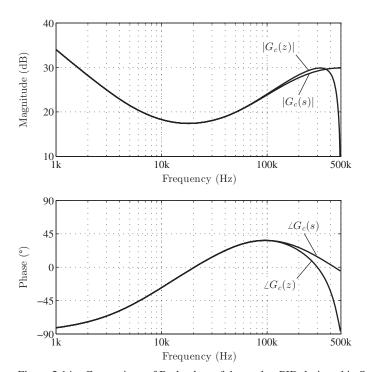

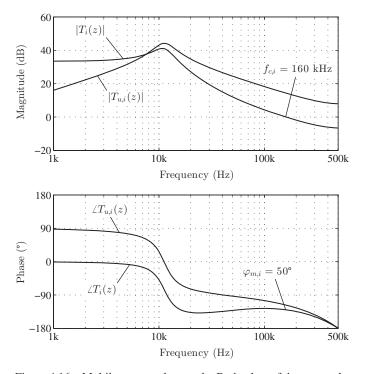

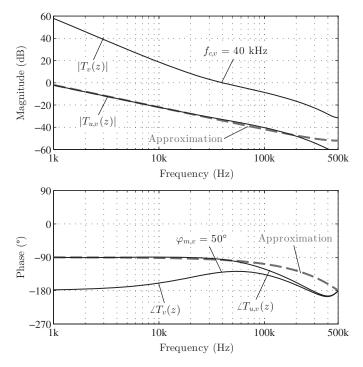

loop, with analog control techniques based on averaged converter models briefly reviewed in Chapter 1. As discussed further in Chapter 2, digital control differs from analog control in two key aspects: time quantization and amplitude quantization. Time quantization refers to the fact that the controller is a discrete-time system that processes sampled versions of sensed analog signals to be regulated and produces a discrete-time control output. In order to design high-performance control loops, it is necessary to understand and consider the resulting delays and aliasing effects. As discussed in Chapters 2 and 3, the use of continuous-time averaged modeling for designing digital loops, an approach often employed in practice, can only account for sampling effects and digital control delays in an approximate manner. A more rigorous approach is based on discrete-time modeling [36], which is described in detail in Chapter 3. This modeling approach enables direct-digital design of compensator transfer functions, which is presented in Chapter 4. The design specifications are presented in frequency domain, in terms of the quantities familiar to the analog designer: the loop-gain crossover frequency  $f_c$  and the phase margin  $\varphi_m$ .

### **Implementation Techniques**

In digitally controlled converters, regulation precision and accuracy are determined by the resolutions of A/D and DPWM blocks, which introduce amplitude quantization effects discussed in Chapter 5. These nonlinear effects can lead to steady-state disturbances commonly referred to as limit cycling [37, 38]. Design guidelines to avoid limit cycling are also presented in Chapter 5, together with a brief summary of high-resolution DPWM and A/D implementation techniques.

Digital compensator implementation is addressed in Chapter 6. Scaling and quantization of compensator coefficients are treated first, with the goal of quantifying the errors introduced by coefficient quantization on the loop gain magnitude and phase at the desired crossover frequency. Chapter 6 then addresses PID compensator structures, such as the parallel PID realization shown in Fig. 2, and the implementation of the control law in a fixed-point arithmetic environment, providing a methodology for word length determination of the various signals inside the control structure. Given the focus of the book on high-frequency switched-mode power converter applications, the emphasis is on *hardwired* implementations of the control law, together with VHDL and Verilog coding examples, while the principles that apply to software-based, microprogrammed realizations are also highlighted.

The objectives of Chapters 1–6 are to enable the reader to successfully analyze, model, design, and implement voltage, current, or multiloop digital feedback loops around switched-mode power converters. Alongside, based on the theoretical concepts, Matlab® scripts are systematically developed, which allow one to rapidly perform discrete-time modeling and system-level compensator design steps, and proceed to implementation steps. Practical examples are used throughout the book to illustrate applications of the techniques developed.

# SYSTEM AND PERFORMANCE GAINS VIA DIGITAL CONTROL

Increased flexibility, programmability, and integration of system interface and power management functions have been recognized as important advantages of digital controllers. Furthermore, as digital controller implementation opened opportunities for practical implementations of more sophisticated control approaches, considerable advances have been made in various directions. This section highlights some of the gains enabled by digital control in the areas of improved dynamic responses, integration of frequency-response measurements, autotuning of digital control loops, and on-line efficiency optimization.

### **Improved Dynamic Responses**

Standard analog or digital converter controller design techniques are based on linear small-signal models and frequency-domain-based compensator designs. It has been recognized that considering the switching nature of the power stage directly, and operating with large-signal instantaneous state variables to provide on—off control actions accordingly, can result in improved dynamic responses. The switching surface control [39] and many other time-domain based approaches have been investigated both in analog and in digital domains. Digital implementation is particularly well suited for explorations of control techniques targeting improved dynamic responses. A case of special interest is a sequence of switching actions that result in minimum time, that is, time-optimal response to an external disturbance such as a step load transient. For example, for a Buck converter, a time-optimal response to a step load transient consists of a single precisely timed on/off sequence. Various digital control methods have been proposed to implement the time-optimal control [34, 35, 40–60].

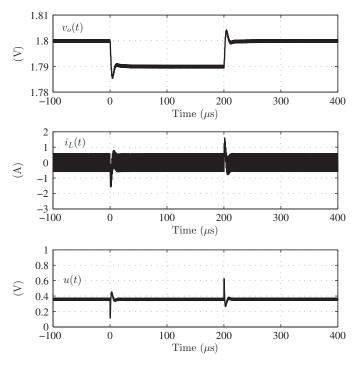

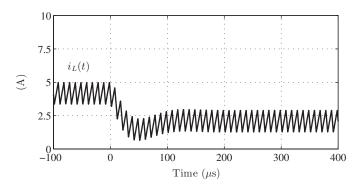

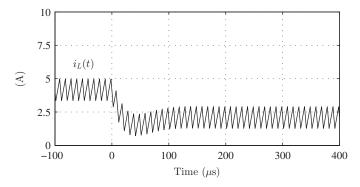

These controllers have demonstrated step load transient responses that approach limits imposed by the converter passive LC filter components. For example, Fig. 4 illustrates the step load transient response of the parameter-independent time-optimal controller described in [34], for the same synchronous Buck prototype as in Fig. 3. The single switching action occurring immediately after the step load is visible, which quickly restores the output voltage to regulation. Compared to the response with the standard PID compensator in Fig. 3, both the voltage deviation and the response time are significantly reduced. As the control action is effectively saturated during time-optimal control events, overshoots may occur in converter internal states such as the inductor current. An extension of digital time-optimal control, including practical inductor current limitations, has been addressed in [57].

A number of other approaches to achieve improved dynamic responses have been explored. Multisampling techniques (where converter waveforms are sampled more than once per switching period [61–63]), asynchronous sampling techniques [35, 64, 65], and mixed-signal control techniques [66, 67] have been proposed to

#### 8

Figure 4 Experimental 0 A-8 A step load response in a digitally controlled POL Buck converter with the time-optimal controller described in [34]  $(v_o: 50 \text{ mV/div}, i_L: 5 \text{ A/div}, \text{ timescale: } 5 \text{ µs/div})$ . © 2009 IEEE.

minimize the control loop delays. Multisampling techniques for constant on-time controllers can also be found in [68–70]. Furthermore, it has been shown that non-linear techniques can lead to dynamic performance improvements in dc–dc [71, 72] and PFC applications [73]. Possibilities for improved dynamic responses in multiphase architectures have been investigated in [74, 75]. More complex controllers in conjunction with power stage modifications present another interesting direction in dynamic responses improvements. For example, it has been shown how digitally controlled power stages with additional auxiliary switches can offer significant dynamic response improvements [76], while [77] takes this approach a step further and proposes a much tighter load-controller interaction.

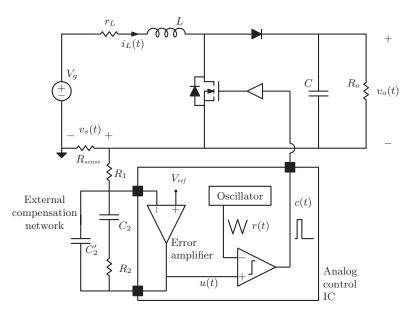

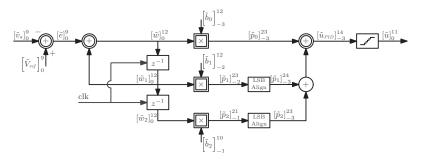

### **Integration of Frequency-Response Measurements**

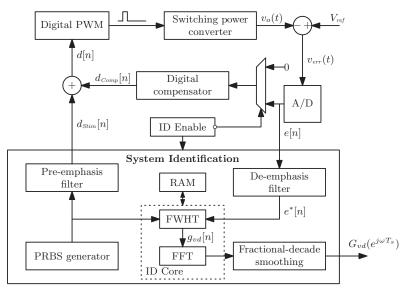

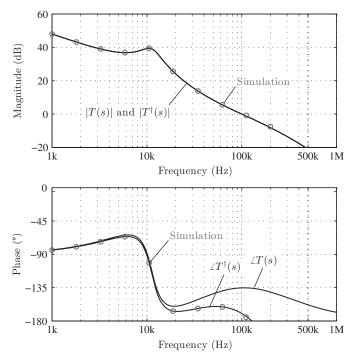

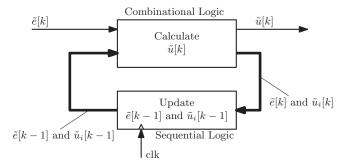

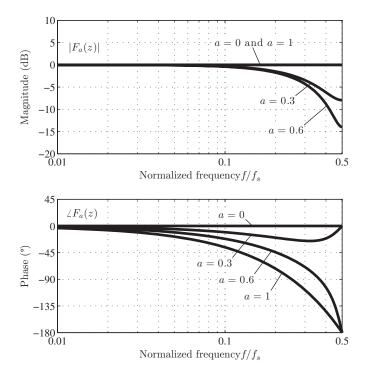

An important experimental verification step in traditional frequency-response-based controller designs includes measuring controller small-signal frequency responses using network analyzers [1, 78]. Feasibility of integrating such nonparametric frequency-domain system identification (system-ID) functionality into digital controllers has been demonstrated in [79, 80]. To briefly summarize the technique, Fig. 5 shows a block diagram of a digitally controlled converter with additional system-ID functions. The identification process consists of perturbing the duty cycle command with a pseudo-random binary sequence (PRBS), cross-correlating the perturbation with the measured output responses to obtain the system impulse response, and performing fast Fourier transform (FFT) to obtain frequency responses. Cross-correlation can be implemented efficiently using the fast Walsh-Hadamard transform (FWHT). Note that the approach reuses the DPWM and the A/D block already present in the digital control loop. To mitigate the effects of switching and quantization noise, the system-ID approach includes a sweep to optimize the perturbation magnitude, pre-emphasis and de-emphasis filters applied to the injected and the sensed signals, respectively, as well as smoothing in the frequency domain. This approach has been applied to a number of converter examples in [80],

Figure 5 Digitally controlled PWM converter with integrated frequency response measurement capabilities [80]. © 2008 IEEE.

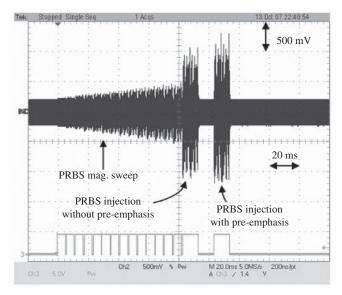

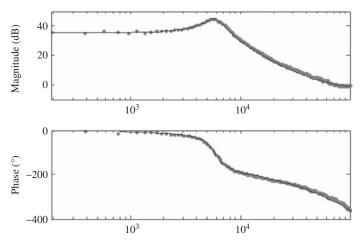

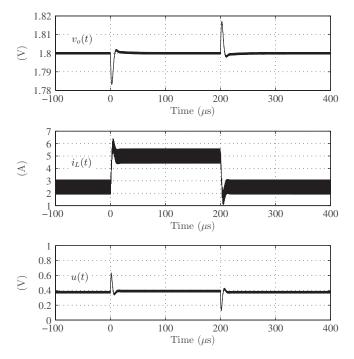

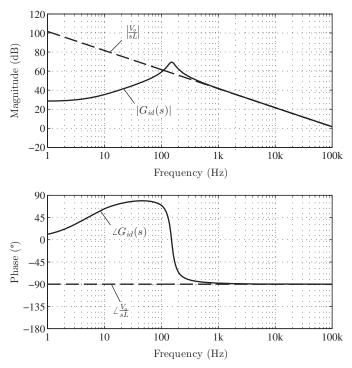

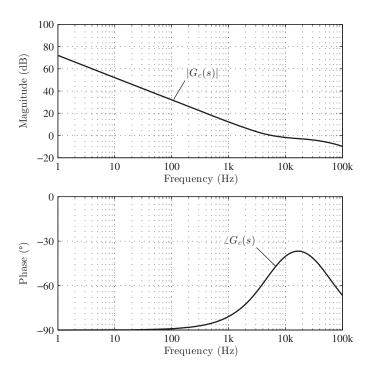

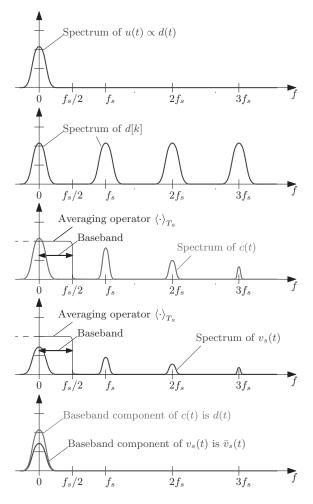

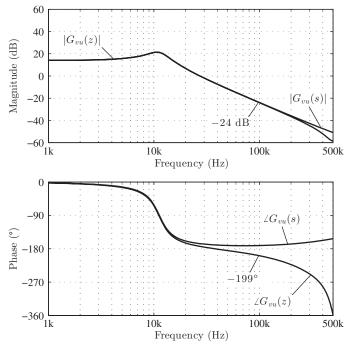

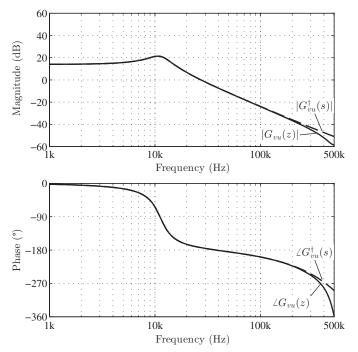

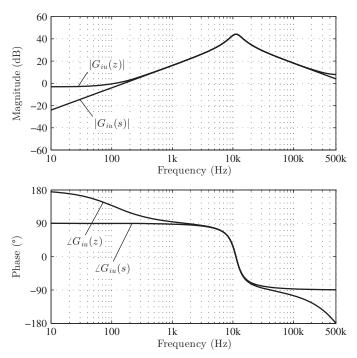

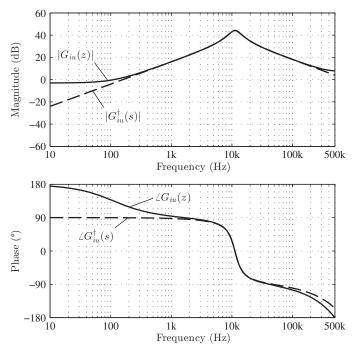

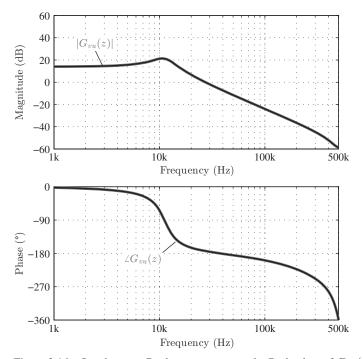

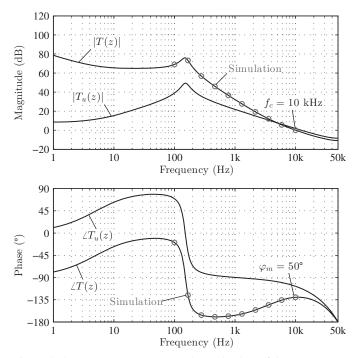

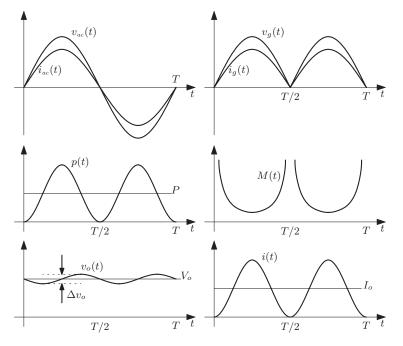

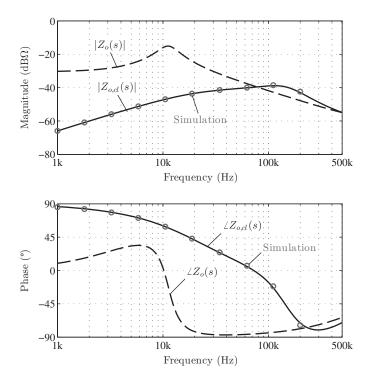

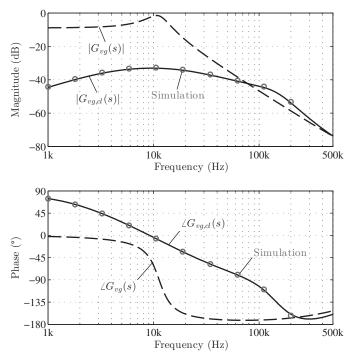

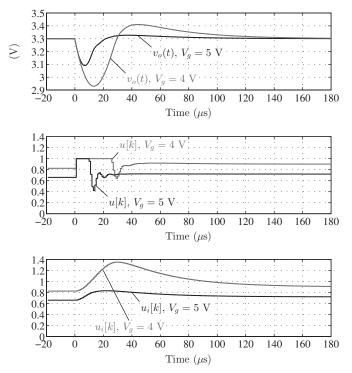

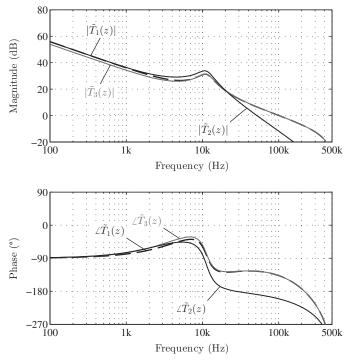

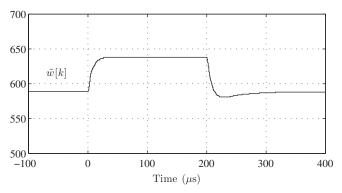

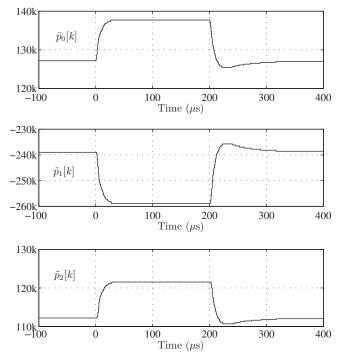

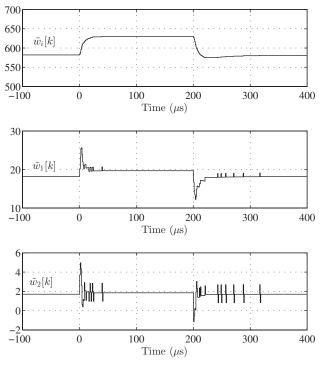

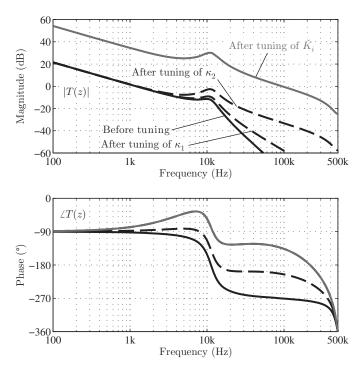

including a 15- to 30-V Boost dc–dc converter operating at  $f_s=195~\rm kHz$ . Figure 6 shows time-domain waveforms during the identification process, while Fig. 7 shows the identified frequency responses, which closely match discrete-time modeling predictions.

The resulting on-line identified frequency response can be used for design, diagnostic, or tuning purposes [81]. The success of these applications depends on the fidelity of the identified frequency responses and the degree to which the process is automated, as well as the costs, in terms of gate count or complexity, time duration of identification, and effects on output voltage, incurred to obtain the results. Reference [80] demonstrates the feasibility of incorporating fully automated frequency response measurement capabilities in digital PWM controllers at relatively low additional cost. The identification process can be typically accomplished in several hundred milliseconds, and the output voltage can be kept within narrow bounds during the entire process.

## **Autotuning**

Taking advantage of the digital controller programmability, the overall objective of autotuning is to automatically tune the controller parameters in response to the actual system dynamics. An autotuning digital controller ideally becomes a "plug and play" unit capable of identifying the key characteristics of the power converter and the load and adjusting the controller parameters to achieve specified performance goals. This capability represents a significant departure from the conventional design flow.

Figure 6 Output voltage during system identification process in a 15- to 30-V Boost dc–dc converter operating at  $f_s=195~\rm kHz$  [80]. © 2008 IEEE.

Figure 7 Control-to-output magnitude and phase responses determined by the system identification process illustrated in Figs. 5 and 6 [80].  $\odot$  2008 IEEE.

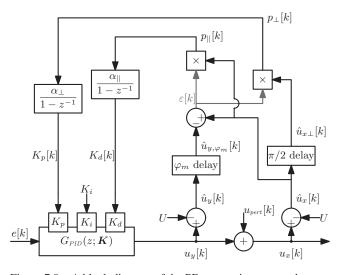

Numerous advances have been made in the area of practical autotuning digital control algorithms and implementation techniques [81–101], and the area is subject to ongoing research and development efforts. Chapter 7 presents an overview of digital autotuning techniques for high-frequency switched-mode power converters. Two autotuning techniques are presented in more detail: an injection-based approach and a relay-based approach.

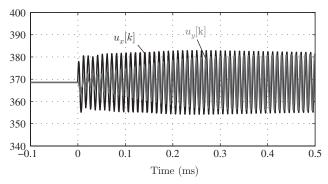

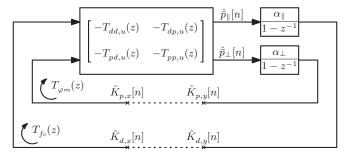

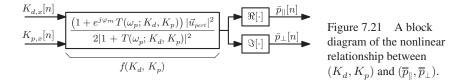

The controller block diagram in Fig. 2 shows how a digital autotuner can be incorporated into the digital controller based on the injection approach [92, 93, 95, 97]. The autotuning system injects a digital perturbation signal  $u_{pert}[k]$  into the feedback loop, superimposed to the PID compensator output  $u_y[k]$ . The overall control command  $u_x[k] = u_y[k] + u_{pert}[k]$  modulates the converter. Simultaneously, signals  $u_y[k]$  and  $u_x[k]$  before and after the injection point are monitored and the tuning process adjusts the compensator gains until the correct amplitude and phase relationships are established between the ac components of  $u_x[k]$  and  $u_y[k]$  at the injection frequency, indicating that the loop gain meets the specifications given in terms of the desired crossover frequency  $f_c$  and phase margin  $\varphi_m$ . The hardware requirements for the entire adaptive tuning system are relatively modest, making it a practical solution.

### **Efficiency Optimization**

Power conversion efficiency is a key performance metric in most applications. In the efficiency improvements area, potential advantages of digital controllers include abilities to precisely adjust switching frequency or other timing parameters of switch control waveforms [27, 102–107], abilities to reconfigure the power stage on-line either through power-switch segmentation [108, 109] or other gate-drive parameters [109, 110], phase shedding [58, 111], or control of current distribution in multiphase architectures [111–113], as well as abilities to implement algorithmic or preprogrammed approaches to on-line efficiency optimization [102, 103, 114–117].

The shift from traditional analog techniques to digital control in high-frequency power electronics is making an impact on standard design practices, as well as in various applications. Programmability, monitoring, digital system interfaces, and system-level power management are becoming ubiquitous in power systems ranging from mobile electronics to desktop computing, data centers, and communication infrastructure. In these systems, digital control further brings opportunities for improved dynamic responses and correspondingly reduced size of passive filters, together with new approaches to converter-level and system-level efficiency optimizations. In response to increasing energy cost and environmental concerns, various energy efficiency initiatives and programs are addressing power conversion efficiency and power quality in data centers and computer power supplies. It is expected that future energy efficiency program specifications will be even more demanding in terms of efficiency, power factor, and harmonic distortion requirements for off-line power supplies over even wider load ranges. Further significant impact can also be expected in renewable energy applications. For example, distributed module integrated converters or micro-inverters in photovoltaic power systems can take advantage of digital control algorithms for improved maximum power point tracking, fault detection, and efficiency optimization. Similar impact can be foreseen in electric-drive vehicles, not just in inverter controls where digital control is already ubiquitous, but also in battery management and battery charger systems.

CHAPTER

# CONTINUOUS-TIME AVERAGED MODELING OF DC-DC CONVERTERS

Converter systems rely on feedback loops to achieve the desired regulation performance. For example, in a typical dc-dc converter application, the objective is to maintain tight regulation of the output voltage in the presence of input voltage or load current variations. An accurate small-signal description of the converter control-to-output dynamics is the starting point for feedback loop design techniques based on frequency-domain concepts of loop gain, crossover frequency, phase margin, and gain margin.

The most successful and widespread modeling technique for switched-mode converters is based on *averaged small-signal modeling* [1, 118–120]. This technique is based on first averaging the converter behavior over a switching period with the purpose of smoothing the discontinuous, time-varying nature of the converter into a continuous, time-invariant nonlinear system model. A successive linearization step yields a linear, time-invariant model that can be treated using standard tools of linear system theory. The converter is described by a *continuous-time linear system*, often presented in the form of a linear equivalent circuit model, a natural representation in the context of analog control design.

The averaging approach is currently the most widely accepted way of *understanding* dynamics of switched-mode power converters. In addition to the relative simplicity and straightforwardness, popularity of the averaging approach has been reinforced by the success of innumerable practical designs supported by robust and easy-to-use integrated circuits for analog converter control.

The main purpose of this chapter is to revisit the main aspects of analysis and modeling techniques for switched-mode power converters. Averaged small-signal modeling, in particular, is reviewed in detail, highlighting the main assumptions behind the approach. This prepares the background necessary to understand the limitations of the averaged small-signal modeling in the context of digital control design and to allow subsequent developments of discrete-time models where these limitations are removed.

A brief review of pulse width modulated (PWM) dc-dc converters is presented in Section 1.1, followed by a summary of steady-state analysis and modeling techniques in Section 1.2. Section 1.3 explains the need for dynamic modeling in the design of control loops around switched-mode power converters and introduces the small-signal averaged modeling approach. The method of state-space averaging [119, 120], a general approach to modeling switched-mode power converters, is summarized in Section 1.4. Analog control design examples are presented in Section 1.5. In the subsequent chapters, these examples are revisited to illustrate modeling and digital control design principles. To complete the background necessary to engage in developments of analysis, modeling and control techniques in the context of digitally controlled PWM converters, a discussion related to the nature of duty cycle, the control variable in PWM converters, is presented in Section 1.6. The key points are summarized in Section 1.7.

### 1.1 PULSE WIDTH MODULATED CONVERTERS

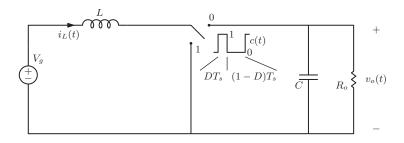

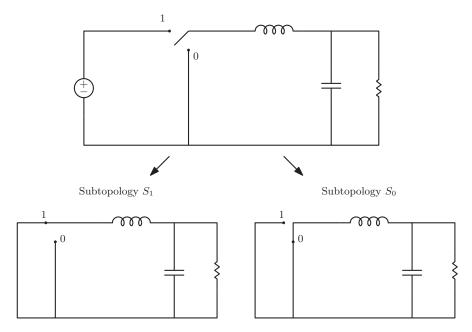

The focus of this book is on *PWM* converters, which are operated so as to alternate between two or more distinct subtopologies in a periodic fashion, with a fundamental *switching period*  $T_s$ . The Boost converter depicted in Fig. 1.1, for instance, operates with the switch in position 1 for a fraction  $DT_s$  of the switching period and with the switch in position 0 for the remaining fraction  $D'T_s \triangleq (1-D)T_s$ . The quantity  $0 \le D \le 1$  is the *duty cycle*, which determines the fraction of a switching period the switch is kept in position 1. In PWM converters, D is the *control input* for the system, which is adjusted by a controller in order to regulate a converter voltage or current.

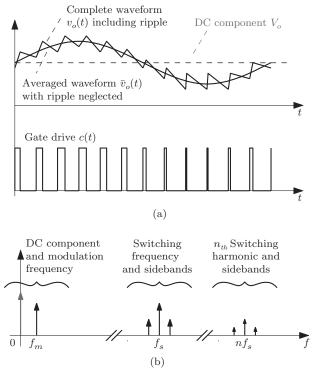

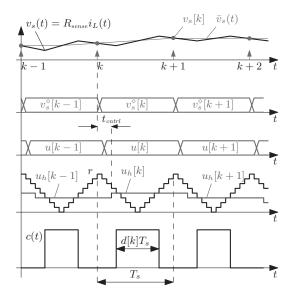

Typical waveforms of a PWM converter are shown in Fig. 1.2, which exemplifies the gate driving signal c(t) and one of the converter state variables, such as the output voltage  $v_o(t)$ . Assuming that the converter duty cycle is sinusoidally modulated at a frequency  $f_m \ll f_s$ , the output voltage consists of a low-frequency component  $\overline{v}_o(t)$ , plus a high-frequency *switching ripple*. The low-frequency component of  $v_o(t)$  contains a dc term  $V_o$  and a spectral component at the modulation frequency  $f_m$ . Using the terminology of modulation theory,  $\overline{v}_o(t)$  is the *baseband* component of  $v_o(t)$ . The high-frequency content, on the other hand, contains the switching frequency  $f_s$  and its harmonics, as well as all the modulation sidebands

Figure 1.1 Pulse width modulated Boost converter.

Figure 1.2 (a) Converter waveforms with duty cycle modulation and (b) qualitative spectrum of a pulse width modulated signal.

originating from nonlinear interactions between  $f_m$  and  $f_s$  components occurring as a result of the modulation process.

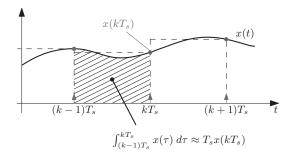

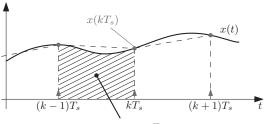

In the context of the averaged modeling approach, the separation between low-frequency and high-frequency portions of the converter signals is of central importance. To be more precise, the *moving average operator*  $\langle \, \cdot \, \rangle_T$  is introduced,

$$\boxed{\langle x(t) \rangle_T \triangleq \frac{1}{T} \int_{t-T/2}^{t+T/2} x(\tau) d\tau}, \tag{1.1}$$

which averages signal x(t) over a period T. With this definition, the low-frequency component  $\overline{v}_o(t)$  of  $v_o(t)$  illustrated in Fig. 1.2 is defined as its moving average over the switching period  $T_s$ ,

$$\boxed{\overline{v}_o(t) \triangleq \langle v_o(t) \rangle_{T_s}}.$$

(1.2)

The fundamental simplification at the basis of the averaging method consists of describing the small-signal dynamics of  $\overline{v}_o(t)$  rather than  $v_o(t)$ , therefore neglecting high-frequency components of the converter waveforms. Both the power and the limitations of the method reside in the averaging approximation.

### 1.2 CONVERTERS IN STEADY STATE

When a converter is operating in steady state, every converter state variable—and therefore every voltage and current—is periodic in time, with a period equal to the converter switching period  $T_s$ . Steady-state operation is reached when all the converter inputs are constant—including the duty cycle—and after all transients are extinguished. In the following text, the basic ideas behind steady-state analysis of PWM converters are summarized. More extensive and detailed treatments can be found in power electronics textbooks [1–5].

Steady-state analysis of switched-mode power converters consists of expressing the dc values of all the voltages and currents in terms of the converter inputs. The analysis is founded on two basic principles, which are direct consequences of the periodicity of the system waveforms:

• *Inductor volt-second balance*. As all the inductor currents are periodic, no net flux variation can occur in any inductor over a switching period,

$$L(i_L(T_s) - i_L(0)) = \int_0^{T_s} v_L(\tau) d\tau = 0.$$

(1.3)

This is equivalent to stating that the average inductor voltage over a switching interval is zero.

$$\boxed{\overline{v}_L(t) = 0} \,. \tag{1.4}$$

Capacitor charge (ampere-second) balance. By a dual argument, as all the

capacitor voltages are periodic, no net charge can be absorbed or delivered by

any capacitor over a switching period,

$$C(v_C(T_s) - v_C(0)) = \int_0^{T_s} i_C(\tau) d\tau = 0.$$

(1.5)

This is equivalent to stating that the average capacitor current over a switching interval is zero,

$$\boxed{\overline{i}_C(t) = 0} \,. \tag{1.6}$$

The two above-mentioned conditions, combined with conventional circuit analysis, are sufficient to solve the steady-state problem. In practice, the calculations are greatly simplified by introducing the *small-ripple approximation*. By *switching ripple*, one refers to the ac component of a converter voltage or current. In steady state, the switching ripple is a periodic function with a fundamental frequency equal to the converter switching rate. The ripple peak-to-peak amplitudes of a capacitor voltage  $v_C(t)$  and an inductor current  $i_L(t)$  are denoted as  $\Delta v_C$  and  $\Delta i_L$ , respectively.

The small-ripple approximation states that the dc converter quantities can be approximately determined by neglecting both capacitors voltage ripples and inductors current ripples. This corresponds to considering every capacitor  ${\cal C}$  as an ideal dc

voltage source of unknown magnitude  $V_C$  and every inductor as a dc current source of unknown magnitude  $I_L$ ,

$$\begin{split} \frac{\Delta v_C}{\overline{v}_C} \ll 1 \Leftrightarrow v_C(t) = V_C = \text{constant} \;, \\ \\ \frac{\Delta i_L}{\overline{i}_L} \ll 1 \Leftrightarrow i_L(t) = I_L = \text{constant} \;. \end{split} \tag{1.7}$$

Contrary to the volt-second balance and the ampere-second balance, which follow directly from the characteristics of inductive and capacitive components and the periodicity of the steady-state operation, the small-ripple approximation is simply a convenient assumption that simplifies the steady-state solution and which is often satisfied in practical converter systems. A relaxed version of the small-ripple approximation, known as linear-ripple approximation, is also often employed. According to the linear-ripple approximation, ripple components of the  $v_{\rm C}(t)$ 's and  $i_{\rm L}(t)$ 's are allowed to be triangular waveshapes. It can be shown that the steady-state analysis proceeds as stated earlier for the small-ripple approximation. In practice, the linear-ripple approximation is easier to meet, especially when considering inductor current waveforms. As long as the small-ripple approximation is satisfied for capacitor voltages, in fact, inductor currents retain triangular waveforms even when the peak-to-peak ripple is not negligibly small compared with the dc component.

It is worth mentioning, at this point, that the above discussion is implicitly focused on the converters operating in *continuous conduction mode* (CCM), where the use of the small-ripple or linear-ripple approximation is well justified for *all* the converter state variables. As for converters operating in *discontinuous conduction mode* (DCM), on the other hand, the above-mentioned assumption does not hold and the analysis becomes somewhat more involved. Further details on DCM modeling can be found in [1, 121–123].

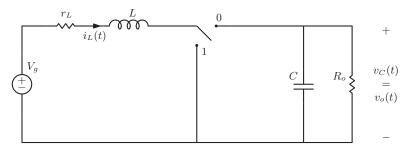

## 1.2.1 Boost Converter Example

As an example, consider the Boost converter depicted in Fig. 1.3. The physical inductor is represented by a series combination of an ideal inductor L and a resistive element  $r_L$ , modeling the inductor copper losses. Other converter components are assumed to be ideal.

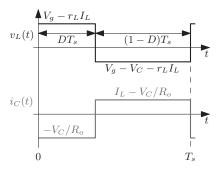

With the switch in position 1 for an interval  ${\cal D}T_s$ , the voltage across the ideal inductor  ${\cal L}$  is

$$v_L(t) = V_g - r_L I_L, (1.8)$$

where the small-ripple approximation  $i_L(t) \approx I_L$  has been employed. In the same topological state and under the small-ripple approximation  $v_C(t) \approx V_C$ , the output capacitor current is

$$i_C(t) = -\frac{V_C}{R_c}. (1.9)$$

Figure 1.3 Boost converter example.

Similarly, with the switch in position 0 for an interval  $D'T_s = (1-D)T_s$ , one has

$$\begin{split} v_L(t) &= V_g - r_L I_L - V_C, \\ i_C(t) &= I_L - \frac{V_C}{R_o}. \end{split} \tag{1.10}$$

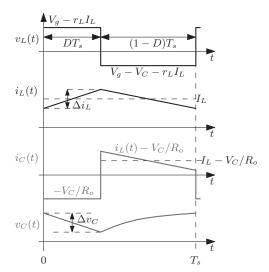

Waveforms  $v_L(t)$  and  $i_C(t)$ , including the small-ripple approximation, are shown in Fig. 1.4. Imposing the volt-second balance (1.4) and the charge balance (1.6), one obtains

$$\begin{split} \overline{v}_L(t) &= D \left( V_g - r_L I_L \right) + D' \left( V_g - r_L I_L - V_C \right) = 0, \\ \overline{i}_C(t) &= D \left( -\frac{V_C}{R_o} \right) + D' \left( I_L - \frac{V_C}{R_o} \right) = 0, \end{split} \tag{1.11}$$

the solution of which is

$$I_{L} = \frac{V_{g}}{D'^{2}R_{o}} \frac{1}{1 + \frac{r_{L}}{D'^{2}R_{o}}},$$

$$V_{C} = \frac{V_{g}}{D'} \frac{1}{1 + \frac{r_{L}}{D'^{2}R_{o}}}.$$

(1.12)

Figure 1.4 Boost converter example: waveforms based on the small-ripple approximation.

The converter *voltage conversion ratio* can be evaluated from the above-mentioned equations as

$$M(D) \triangleq \frac{V_o}{V_g} = \frac{V_C}{V_g} = \frac{1}{D'} \frac{1}{1 + \frac{r_L}{D'^2 R_o}},$$

(1.13)

which reduces to the familiar Boost M(D) = 1/D' for a lossless converter  $(r_L = 0)$ .

### 1.2.2 Estimation of the Switching Ripple

Once the dc converter quantities are determined, one can go back to the converter topology and estimate both the waveshapes and the amplitudes of the steady-state inductor current and capacitor voltage ripples.

In the Boost converter example, as shown in Fig. 1.4, the inductor voltage waveform  $v_L(t)$  is approximately a piecewise-constant signal. The inductor current ripple is therefore a triangular waveform with slopes determined by  $v_L(t)$ . Neglecting, for simplicity, the inductor series resistance  $r_L$ , the peak-to-peak current ripple  $\Delta i_L$  can be determined by integrating  $v_L(t)/L$  over either one of the two switching subintervals,

$$\Delta i_L = \frac{1}{L} \int_0^{DT_s} v_L(\tau) d\tau = \frac{V_g}{L} DT_s = \frac{T_s}{L} V_g \left( 1 - \frac{V_g}{V_o} \right). \tag{1.14}$$

Similarly, one can reconstruct the capacitor voltage ripple waveshape by integration of  $i_C(t)$  shown in Fig. 1.4. More accurate results can be obtained by removing the small-ripple approximation and by deriving  $i_C(t)$  using, this time, the triangular waveshape  $i_L(t)$  determined earlier. The corresponding waveforms are depicted in Fig. 1.5.

Figure 1.5 Boost converter example: estimation of the ripple waveshapes.

To determine the peak-to-peak output voltage ripple, similar to finding  $\Delta i_L$ , one can directly integrate  $i_C(t)/C$  over either one of the two switching subintervals,

$$\Delta v_C = \frac{1}{C} \int_0^{DT_s} |i_C(\tau)| \, d\tau = \frac{V_o}{R_o C} DT_s = \frac{T_s}{R_o C} \left( V_o - V_g \right). \tag{1.15}$$

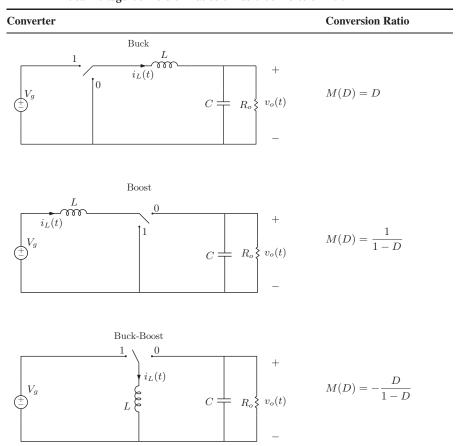

### 1.2.3 Voltage Conversion Ratios of Basic Converters

Systematic application of the volt-second and charge balance equations, along with the small-ripple approximation, allows straightforward steady-state analysis of any PWM converter. Table 1.1 reports the CCM conversion ratios of the three basic converter topologies in the ideal (lossless) case.

TABLE 1.1 Ideal Voltage Conversion Ratios of Basic Converters in CCM

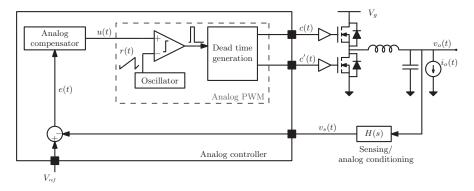

Figure 1.6 Analog voltage-mode control of a synchronous Buck converter.

### 1.3 CONVERTER DYNAMICS AND CONTROL

The main topic of this chapter—converter averaged small-signal modeling—is now discussed. Consider voltage-mode control of a synchronous Buck converter as a simple case study to review the basic concepts of the approach. A block diagram of the system is illustrated in Fig. 1.6. The term *synchronous* referred to the Buck converter is associated with the implementation of the rectifying, or secondary, switch: instead of the usual free-wheeling diode used as a passive rectifier, the Buck converter of Fig. 1.6 makes use of a *controlled* switch that is driven by the complementary version c'(t) of the PWM signal,

$$c'(t) \triangleq 1 - c(t). \tag{1.16}$$

A primary advantage of synchronous rectification is the smaller voltage drop across the rectifier switch during conduction, as opposed to the diode rectifier, an essential requirement when regulating low output voltages. Furthermore, the rectifier switch becomes *current bidirectional*, therefore guaranteeing CCM operation and converter controllability even at no load.

In Fig. 1.6, the load is represented by an independent current source rather than a resistance. This is an appropriate modeling choice for many digital loads in point-of-load applications, in which the converter output current depends on the load internal activity and is independent of the output voltage.

The converter is feedback-controlled in order to achieve regulation of the output voltage  $v_o(t)$  at a constant reference value  $V_{ref}$ . To this end, a control error e(t) is found as the difference between the analog setpoint  $V_{ref}$  and the sensed signal  $v_s(t)$ , where  $v_s(t)$  is a scaled, filtered version of  $v_o(t)$ . In Fig. 1.6, sensing, scaling, and analog filtering of  $v_o(t)$  are modeled by the transfer function H(s).

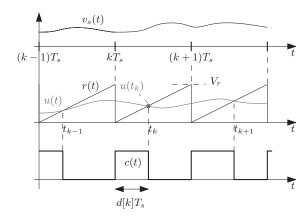

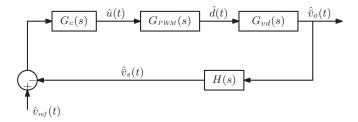

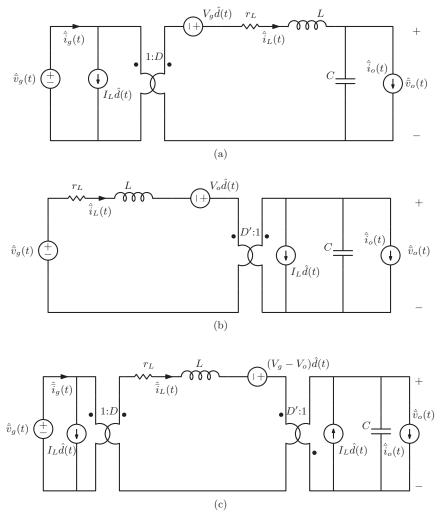

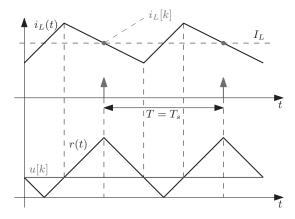

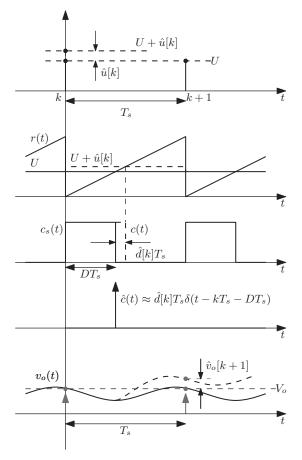

The analog continuous-time compensator processes the error signal and outputs a control command u(t). As exemplified in Fig. 1.7, u(t) is then compared with the carrier r(t) of a trailing-edge pulse width modulator, which in turn produces the modulated gate drive signal c(t).

Figure 1.7 Typical analog control waveforms.

The end goal of the modeling step is the derivation of an equivalent small-signal model of the control loop. The process involves, as anticipated, averaging and linearizing the converter behavior around the above steady-state operating point. In the following, notation (1.2) is employed to denote converter quantities averaged over a switching period.

### 1.3.1 Converter Averaging and Linearization

Referring to the Buck converter shown in Fig. 1.8(a) and applying the moving average operator (1.1) to voltage  $v_x$  at the switching node, one has

$$\overline{v}_x(t) \approx d(t)\overline{v}_g(t),$$

(1.17)

while the averaged converter input current  $\overline{i}_g$  is

$$\overline{i}_q(t) \approx d(t)\overline{i}_L(t).$$

(1.18)

These results<sup>1</sup> allow construction of an *averaged equivalent circuit*, as shown in Fig. 1.8(b) [1], which is now time-invariant but still nonlinear.

Perturbation of the circuit equations around the steady-state operating point and successive linearization yields

$$\begin{split} \hat{\overline{v}}_x(t) &\approx D \hat{\overline{v}}_g(t) + V_g \hat{d}(t), \\ \hat{\overline{i}}_g(t) &\approx D \hat{\overline{i}}_L(t) + I_L \hat{d}(t), \end{split} \tag{1.19}$$

$<sup>^1</sup>$  Approximation  $\langle c(t)x(t)\rangle_{T_s}\approx d(t)\langle x(t)\rangle_{T_s}$  is justified, in general, whenever x(t) has negligible switching content, that is, when it can be regarded as an essentially baseband signal. One exception to this occurs when x(t) has a triangular switching ripple, in which case the approximation is justified even in the presence of a large ripple component. In conclusion, one can safely assume  $\langle c(t)x(t)\rangle_{T_s}\approx d(t)\langle x(t)\rangle_{T_s}$  under the small-ripple or linear-ripple approximations already discussed in Section 1.2.

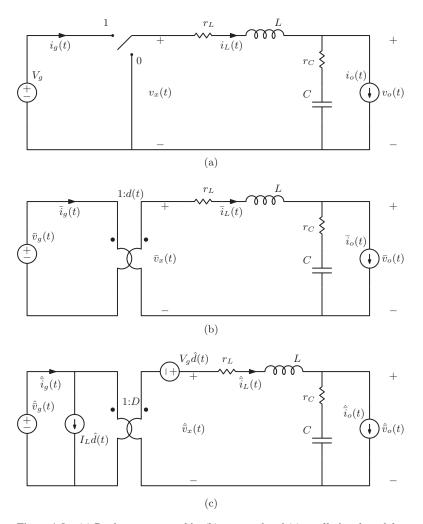

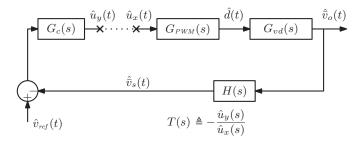

Figure 1.8 (a) Buck converter and its (b) averaged and (c) small-signal models.

where  $\hat{\overline{x}}(t) = \overline{x}(t) - X$  denotes the small-signal component of  $\overline{x}(t)$  with respect to the dc component X. Figure 1.8(c) illustrates the averaged, small-signal equivalent circuit of the Buck converter obtained after the linearization process. From the equivalent circuit model, evaluation of the control-to-output transfer function  $G_{vd}(s)$  yields

$$G_{vd}(s) \triangleq \frac{\hat{\overline{v}}_o(s)}{\hat{d}(s)} \bigg|_{\hat{\overline{v}}_g = 0, \hat{\overline{t}}_o = 0} = V_g \frac{1 + sr_C C}{1 + s(r_C + r_L)C + s^2 LC}$$

$$= G_{vd0} \frac{1 + \frac{s}{\omega_{ESR}}}{1 + \frac{s}{O\omega_0} + \frac{s^2}{\omega_0^2}}, \tag{1.20}$$

with

$$\begin{split} G_{vd0} &\triangleq V_g, \\ \omega_{ESR} &\triangleq \frac{1}{r_C C}, \\ \omega_0 &\triangleq \frac{1}{\sqrt{LC}}, \\ Q &\triangleq \frac{1}{r_C + r_L} \sqrt{\frac{L}{C}}. \end{split} \tag{1.21}$$

The converter small-signal behavior is therefore that of a second-order system with resonant frequency and Q-factor  $(\omega_0,Q)$ , and with a real left half-plane (LHP) zero located at  $s=-\omega_{ESR}$ . The zero originates from the equivalent series resistance (ESR)  $r_C$  of the output capacitor.

### 1.3.2 Modeling of the Pulse Width Modulator

A small-signal model of the pulse width modulator is necessary in order to develop a complete small-signal model of a converter system. This topic is particularly important as there are significant differences in the PWM small-signal dynamics between analog and digital control.

There are two main families of pulse width modulators:

- Naturally sampled pulse width modulators (NSPWMs) process a continuoustime modulating signal u(t). They are commonly employed in analog controllers.

- Uniformly sampled pulse width modulators (USPWMs) are characterized by a discrete-time modulating signal u[k], which is updated once every switching period and held constant throughout the entire switching interval during its comparison with the PWM carrier. USPWMs are most commonly employed in digital control loops, where the control signal is inherently discrete in time, as detailed further in the following chapters. It is worth mentioning, however, that it is possible to apply uniformly sampled modulation in analog control: the continuous-time control command u(t) is in this case subject to a sample & hold operation, the output of which is then compared with the PWM carrier using an analog comparator.

Consider a naturally sampled PWM employed in analog, continuous-time control loop around a switched-mode converter. As illustrated in Fig. 1.7, the duty cycle d[k] applied to the power converter during the kth switching cycle is equal to

$$d[k] = \frac{u(t_k)}{V_r},\tag{1.22}$$

where  $t_k$  represents the instant at which u(t) intersects the PWM carrier r(t) during the kth switching cycle, while  $V_r$  is the PWM carrier amplitude. Duty cycle d[k] during the kth switching cycle therefore corresponds to a *sampled* version of the

modulating signal u(t). Sampling occurs as a result of the intersection between u and r and is inherent to the PWM process—this is the main reason why these types of modulator are designated as  $naturally\ sampled$ . For small perturbations  $\hat{u}$  around a steady-state value U, every sampling instant occurs at the same position in the switching interval, and the equivalent sampling performed by the PWM becomes uniform.

From (1.22), one also has that d[k] is determined by the *instantaneous* value of u(t) at its intersection with the PWM carrier. The absence of any delay between the natural sampling of u(t) operated by the modulator and the generation of the PWM modulated edge justifies, at least on an intuitive level, the common practice in analog control modeling to treat the PWM as a simple gain block. Denoting with  $\hat{u}$  and  $\hat{d}$  the control command and duty cycle small-signal components with respect to their steady-state values, the PWM transfer function is therefore

$$G_{PWM}(s) \triangleq \frac{\hat{d}}{\hat{u}} = \frac{1}{V_r}.$$

(1.23)

It should be noted that (1.23) neglects propagation delays in the PWM comparator and in the gate driving circuitry between the pulse width modulator and the power switch. Such delays, however, are usually much shorter than the switching period  $T_{\rm s}$ . It follows that:

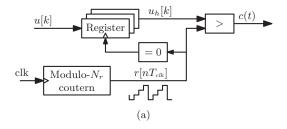

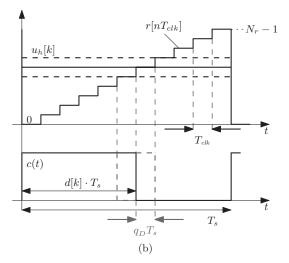

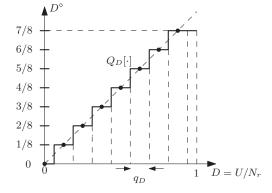

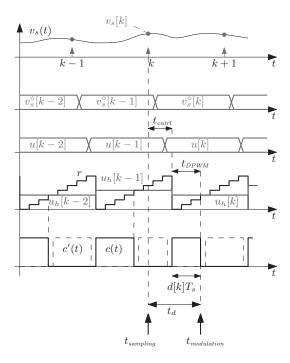

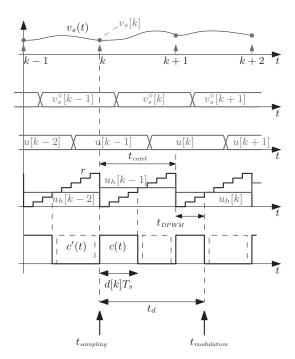

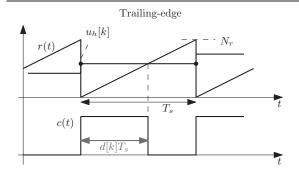

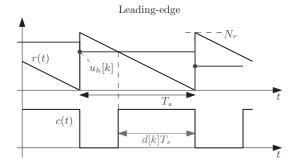

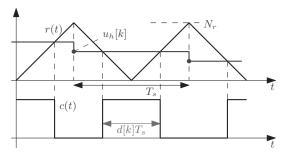

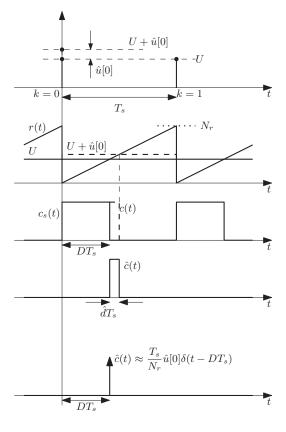

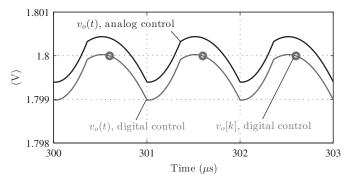

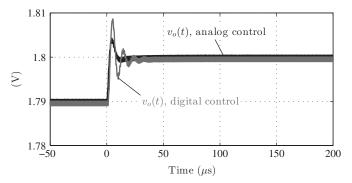

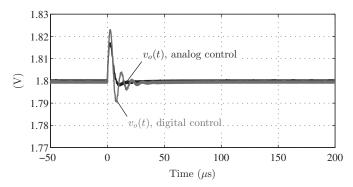

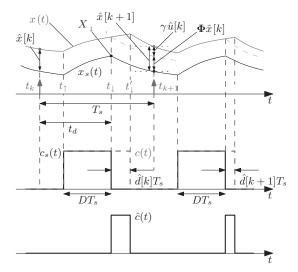

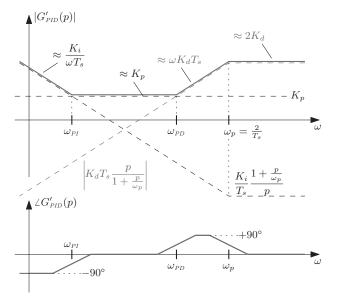

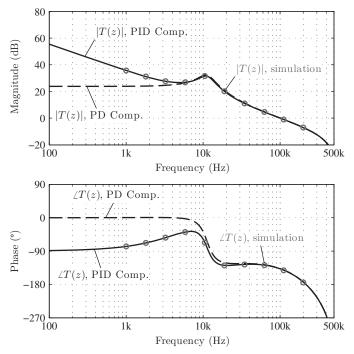

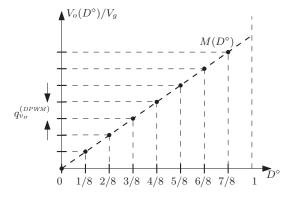

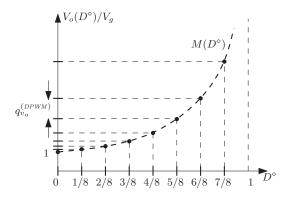

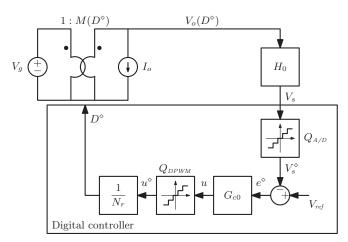

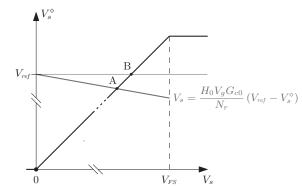

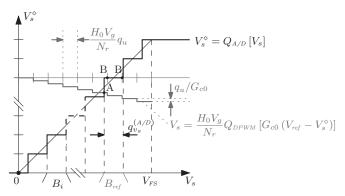

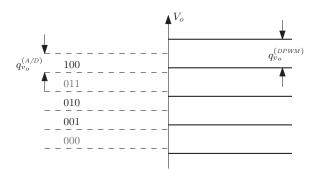

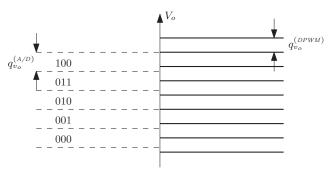

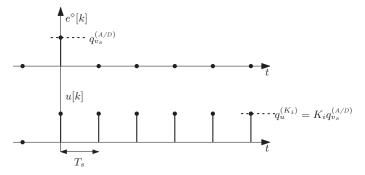

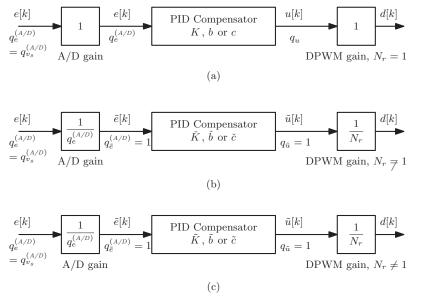

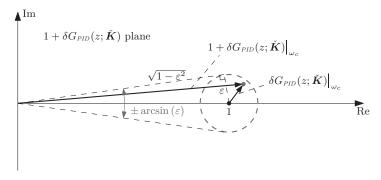

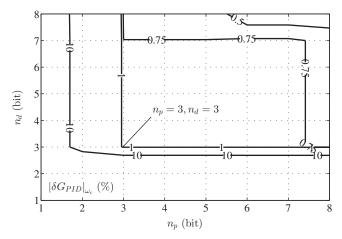

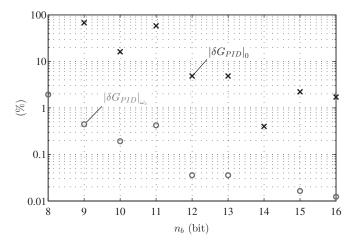

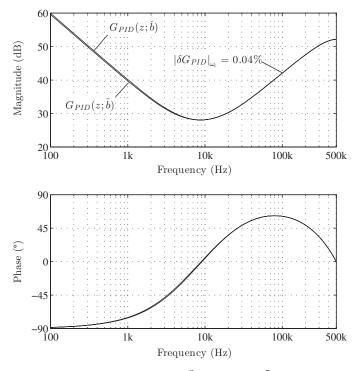

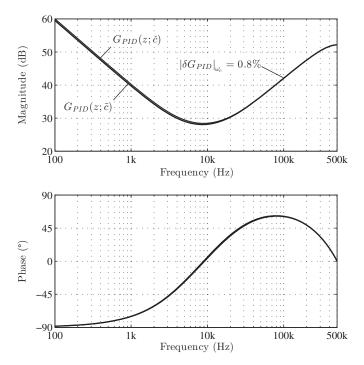

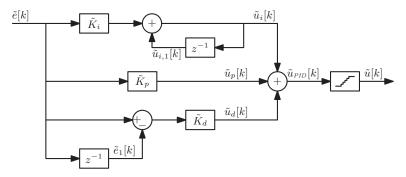

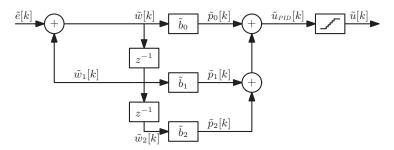

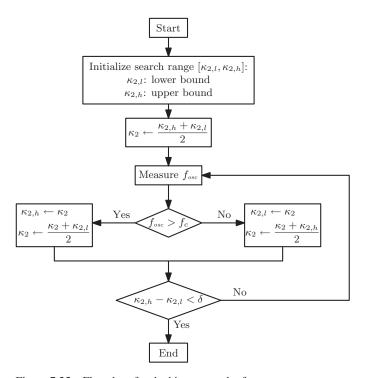

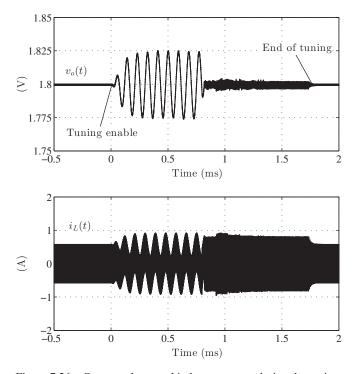

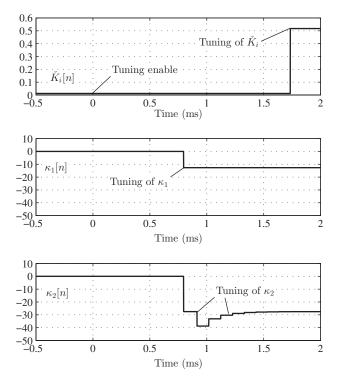

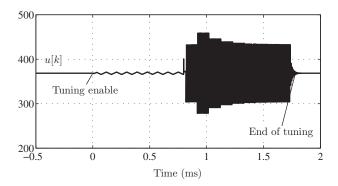

Naturally sampled PWMs do not contribute to the small-signal dynamics of the control loop, except for a constant gain factor.